Intel CONTROLLERS 413808 User Manual

Page 145

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

145

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

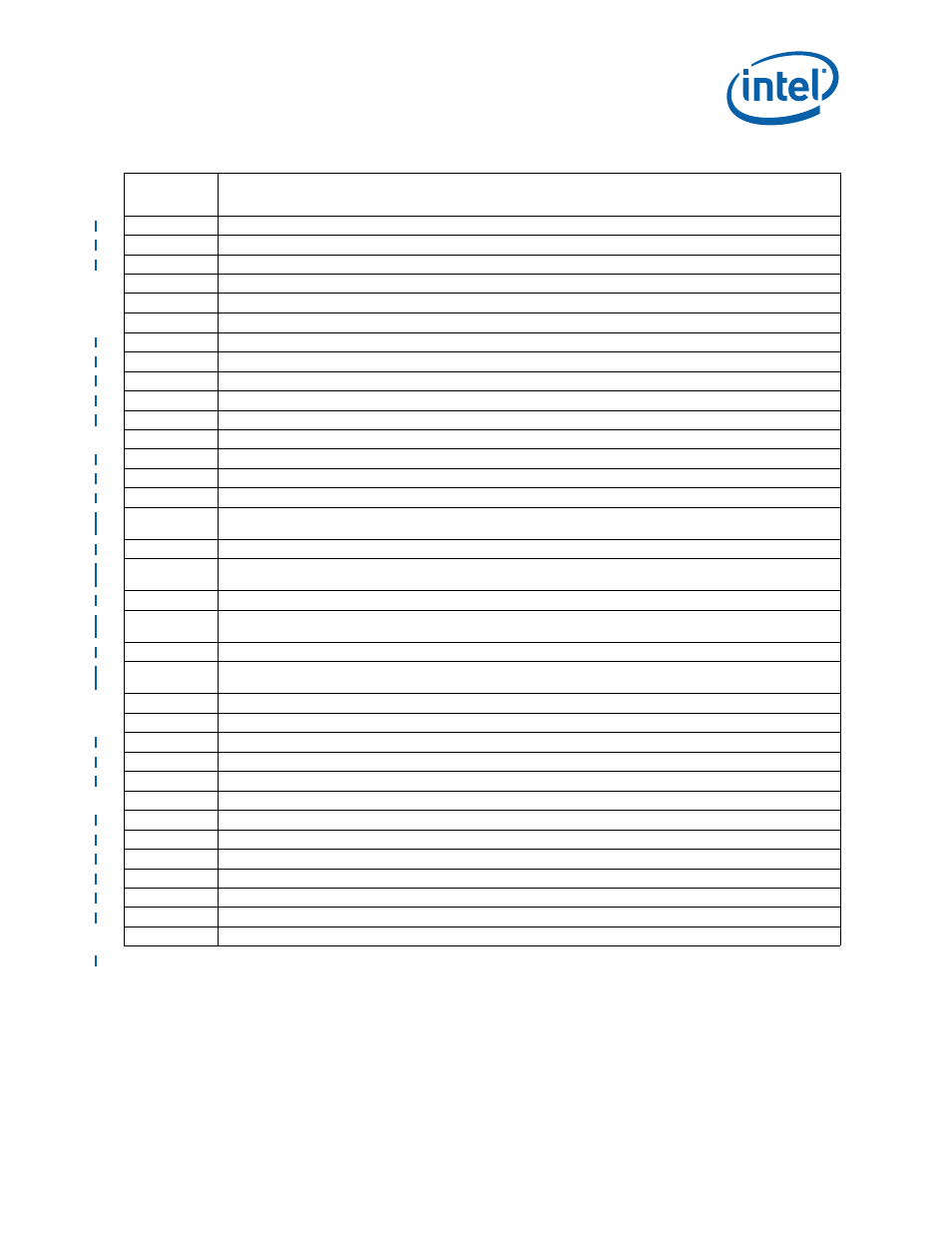

0E8H

Section 2.14.61, “CompactPCI Hot-Swap Capability ID Register” on page 200

0E9H

Section 2.14.62, “Offset EDh: HS_NXTP - Next Item Pointer” on page 201

0EAH

Section 2.14.63, “HS_CNTRL - Hot-Swap Control/Status Register” on page 202

0EBH

Reserved

0ECH — 0FFH Reserved

100H — 1FFH Reserved

200H

Section 2.14.64, “Inbound ATU Base Address Register 3 - IABAR3” on page 204

204H

Section 2.14.65, “Inbound ATU Upper Base Address Register 3 - IAUBAR3” on page 205

208H

Section 2.14.66, “Inbound ATU Limit Register 3 - IALR3” on page 206

20CH

Section 2.14.67, “Inbound ATU Translate Value Register 3 - IATVR3” on page 207

210H

Section 2.14.68, “Inbound ATU Upper Translate Value Register 3 - IAUTVR3” on page 207

214H — 2FCH Reserved

300H

Section 2.14.69, “Outbound I/O Base Address Register - OIOBAR” on page 208

304H

Section 2.14.70, “Outbound I/O Window Translate Value Register - OIOWTVR” on page 209

308H

Section 2.14.71, “Outbound Upper Memory Window Base Address Register 0 - OUMBAR0” on page 210

30CH

Section 2.14.72, “Outbound Upper 32-bit Memory Window Translate Value Register 0 - OUMWTVR0” on

310H

Section 2.14.73, “Outbound Upper Memory Window Base Address Register 1 - OUMBAR1” on page 212

314H

Section 2.14.74, “Outbound Upper 32-bit Memory Window Translate Value Register 1 - OUMWTVR1” on

318H

Section 2.14.75, “Outbound Upper Memory Window Base Address Register 2 - OUMBAR2” on page 214

31CH

Section 2.14.76, “Outbound Upper 32-bit Memory Window Translate Value Register 2 - OUMWTVR2” on

320H

Section 2.14.77, “Outbound Upper Memory Window Base Address Register 3 - OUMBAR3” on page 216

324H

Section 2.14.78, “Outbound Upper 32-bit Memory Window Translate Value Register 3 - OUMWTVR3” on

328H

Reserved

32CH

Reserved

330H

Section 2.14.79, “Outbound Configuration Cycle Address Register - OCCAR” on page 218

334H

Section 2.14.80, “Outbound Configuration Cycle Data Register - OCCDR” on page 219

338H

Section 2.14.81, “Outbound Configuration Cycle Function Number - OCCFN” on page 219

33CH — 37CH Reserved

380H

Section 2.14.82, “PCI Interface Error Control and Status Register - PIECSR” on page 220

384H

Section 2.14.83, “PCI Interface Error Address Register - PCIEAR” on page 221

388H

Section 2.14.84, “PCI Interface Error Upper Address Register - PCIEUAR” on page 222

38CH

Section 2.14.85, “PCI Interface Error Context Address Register — PCIECAR” on page 223

394H

Section 2.14.86, “Internal Arbiter Control Register - IACR” on page 224

398H

Section 2.14.87, “Multi-Transaction Timer - MTT” on page 225

39CH

Reserved.

a. All MSI and MSI-X capability register descriptions are in

Section 4.7, “Register Definitions” on page 410

of

Table 26. Address Translation Unit Registers (Sheet 3 of 3)

Register

Offset

ATU Register Section, Name, Page