11 hosttolocal byte count register - h2l_bcr, 309 hosttolocal byte count register - h2l_bcr, Intel – Intel CONTROLLERS 413808 User Manual

Page 454: Bit default description, Intel xscale

Intel

®

413808 and 413812—SRAM DMA Unit (SDMA)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

454

Order Number: 317805-001US

5.4.11

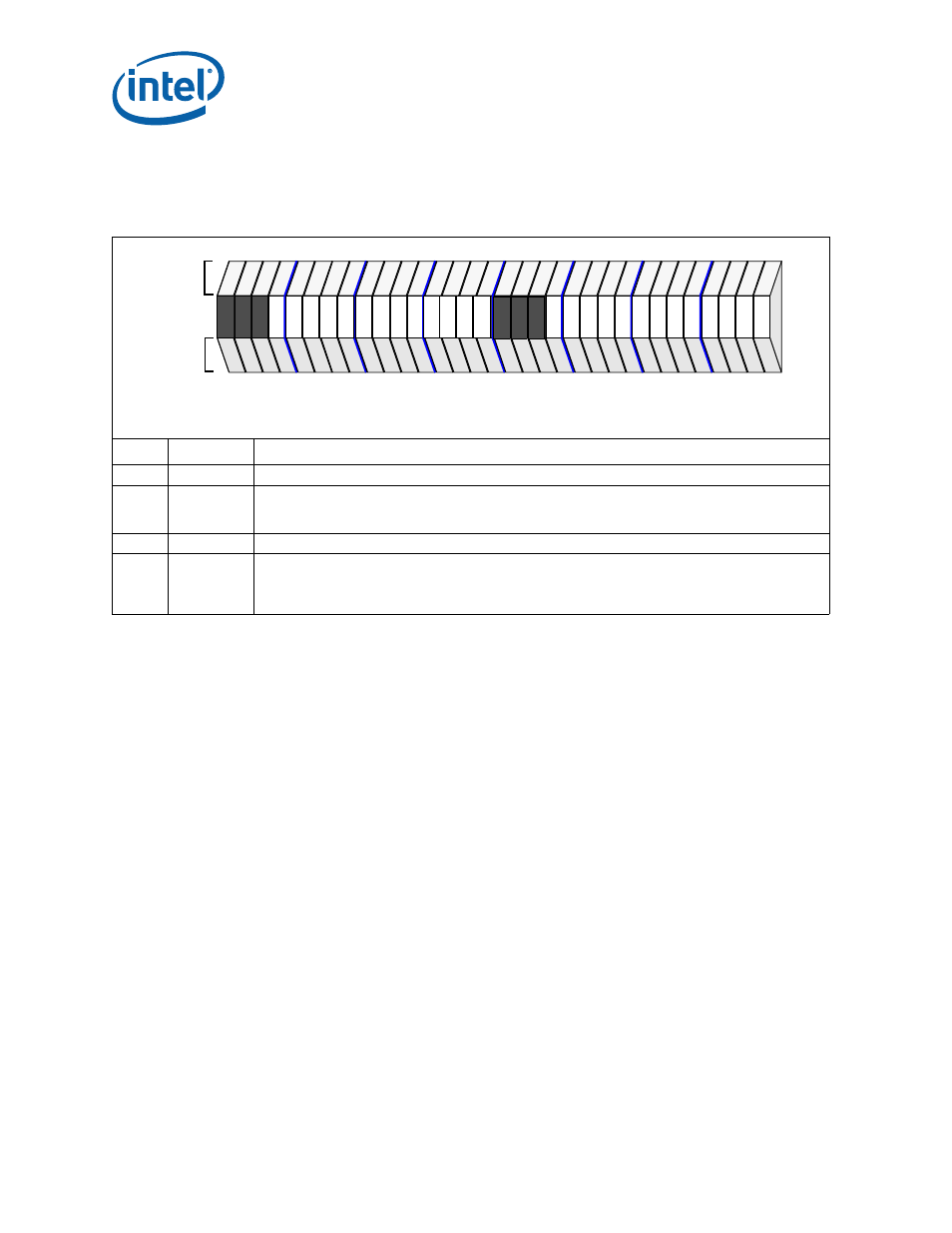

HostToLocal Byte Count Register - H2L_BCR

The HostToLocal Byte Count Registers (H2L_BCR) represent the byte count of the DMA.

Table 309. HostToLocal Byte Count Register - H2L_BCR

Bit

Default

Description

31:29

000

2

Reserved

28:16

00000H

Byte Count Register (BCR)

This field specifies the length in bytes that is for the data to be transferred. The maximum transfer count

value is 4096 bytes (1000H). This field is CLEARED by a hardware or software reset.

15:13

000

2

Reserved. Must be written as zero.

12:00

000H

Byte Count Register (BCR)

This field specifies the length in bytes that is for the data to be transferred. The maximum transfer count

value is 4096 bytes (1000H). This field is CLEARED by a hardware or software reset. This must be

written the same as bits 28:16, otherwise unpredictable results occur.

Coprocessor

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

Intel XScale

®

Microarchitecture internal bus address

offset

18268H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible