Intel, Bit default description, Reserved. 00 0 – Intel CONTROLLERS 413808 User Manual

Page 502

Intel

®

413808 and 413812—System Controller (SC) and Internal Bus Bridge

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

502

Order Number: 317805-001US

7.5.3

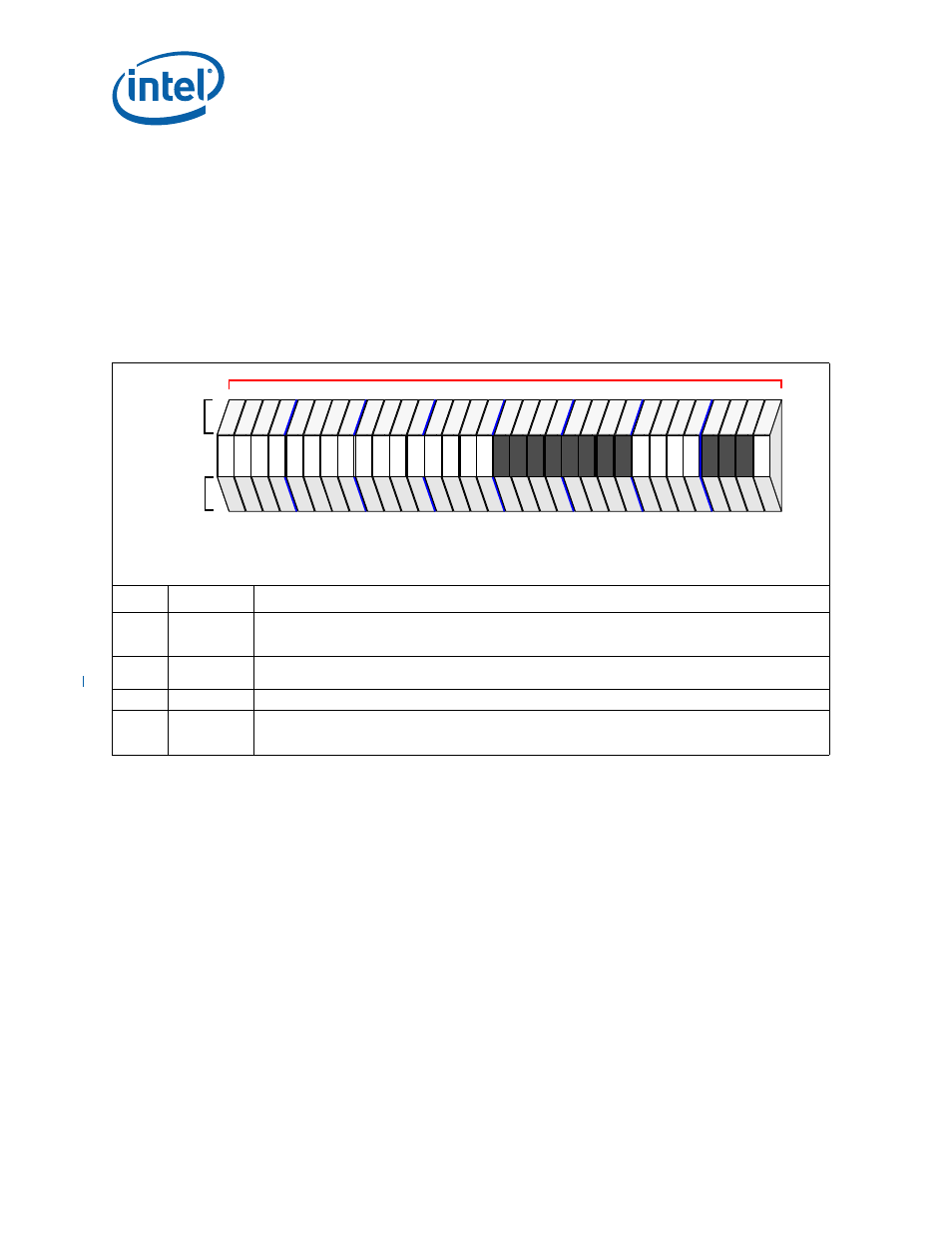

South Internal Bus Data Test Control Register — SIBDTCR

The SIBDTCR can be used to inject a data parity error on the south internal data bus.

The user must provide the ID of the initiator and also set the enable bit. The enable bit

(when set) is used by hardware to inject a data parity error on the next data

transaction provided the programmed ID matches. The parity error is injected in the

first data phase. The enable bit is cleared by hardware in the cycle that follows the first

data phase. This is done to prevent recurring parity errors.

Note:

In order to inject the data parity error in the desired transaction, the user must try to

write this register immediately before the transaction is issued on the internal bus.

Table 336. South Internal Bus Data Test Control Register — SIBDTCR

Bit

Default

Description

31:16

0000

2

Data Parity Mask bits — Each bit of the generated data parity is XORed with the appropriate bits in this

mask field before the parity bits are driven on the south internal bus. Bit16 corresponds to data parity

bit 0, bit 17 corresponds to data parity bit 1, and so on.

07:04

0000

2

Initiator ID — This field specifies the initiator ID of the data (for example, the unit sourcing the data).

Refer to

Table 331, “Data Parity Testing Completer IDs” on page 489

for the initiator IDs.

03:01

000

2

Reserved.

00

0

2

Enable bit — When this bit is set, a data parity error is injected on the next data request made when the

initiator ID of the transaction matches the specified Initiator ID in bits[07:04] of this register. This bit is

set by software and cleared by hardware.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rw

na

rw

na

rw

na

rv

na

rv

na

rv

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

South XBG

internal bus address offset

+1648H