4 bus width, Figure 63. data width and low order address lines, 63 data width and low order address lines – Intel CONTROLLERS 413808 User Manual

Page 548: D[7:0, D[15:0, A[1:0, A[2:1, D[15:8, Bit data is placed on lines

Intel

®

413808 and 413812—Peripheral Bus Interface Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

548

Order Number: 317805-001US

9.2.4

Bus Width

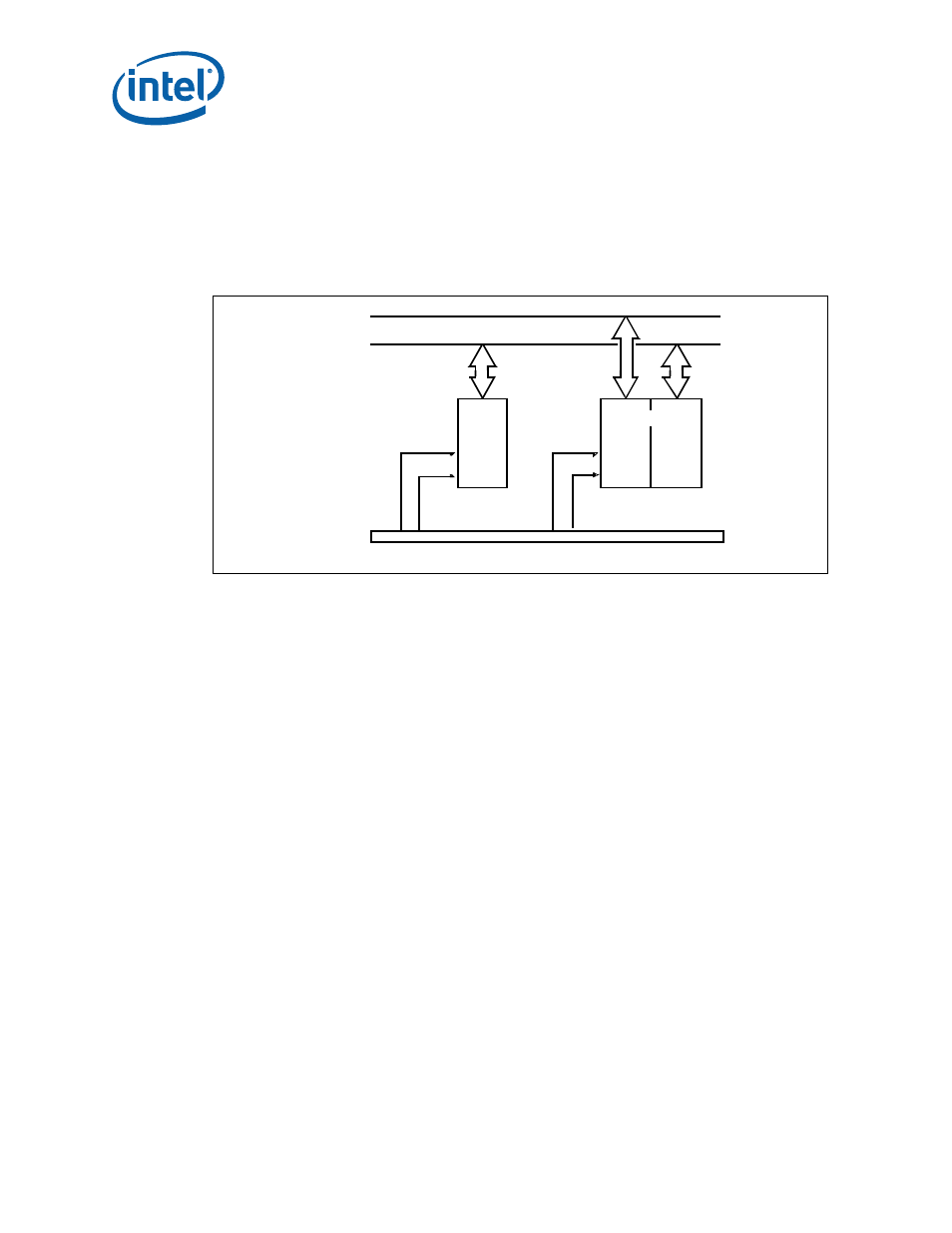

Each address range’s attributes are programmed in the PBIs boundary registers. The

PBI allows an 8-, or 16-bit data bus width for each range. The PBI places 8- and 16-bit

data on low-order data signals, simplifying the interface to narrow bus external

, 8-bit data is placed on lines

D[7:0]

; 16-bit data is

placed on lines

D[15:0]

.

The user needs to wire up the flash memories in a manner consistent with the

programmed bus width:

• 8-bit region:

A[1:0]

provide the demultiplexed byte address for a read burst.

• 16-bit region:

A[2:1]

provide the demultiplexed short-word address for a read

burst.

During initialization, bus width is selected for each of the two address ranges in the

Peripheral Base Address Registers (PBBAR0 — PBBAR1). In addition, the

PBBAR0-PBBAR1 can be used to configure these ranges as Peripheral Windows and to

set a Wait state profile.

The PBI drives determinate values on all address/data signals during T

W

/T

D

write

operation states. For an 8-bit bus, the PBI continues to drive address on unused data

signals

D[15:8]

.

Figure 63. Data Width and Low Order Address Lines

D[15:8]

D[7:0]

A1

A0

A[2:0]

A2

A0

A1

16 - Bit

8 - Bit

A1

A1

A2

B6266-01