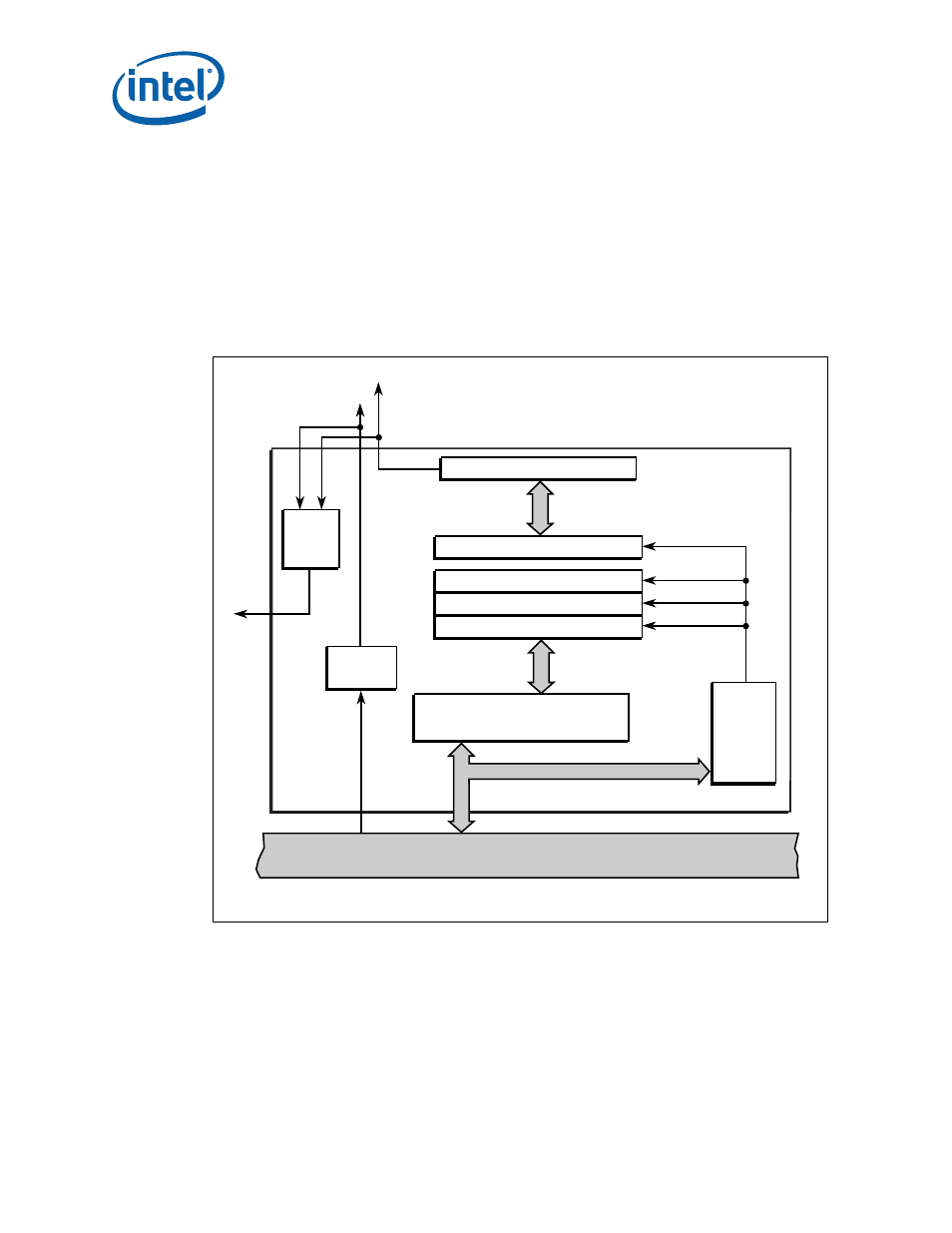

1 operational blocks, Figure 92. i2c bus interface unit block diagram, 92 i – Intel CONTROLLERS 413808 User Manual

Page 692: Figure 92. i, C bus interface unit block diagram, The i, Intel, C bus interface units

Intel

®

413808 and 413812—I

2

C Bus Interface Units

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

692

Order Number: 317805-001US

14.2.1

Operational Blocks

The I

2

C Bus Interface Unit is a slave peripheral device that is connected to the internal

bus. The 4138xx interrupt mechanism can be used for notifying the 4138xx that there

is activity on the I

2

C bus. Polling can be also be used instead of interrupts, although it

would be very cumbersome.

shows a block diagram of the I

2

C Bus Interface

Unit and its interface to the internal bus.

The I

2

C Bus Interface Unit consists of the two wire interface to the I

2

C bus, an 8-bit

buffer for passing data to and from the 4138xx, a set of control and status registers,

and a shift register for parallel/serial conversions.

Figure 92. I

2

C Bus Interface Unit Block Diagram

A8280-01

Internal Bus

Internal Bus Address & Control Signals

Data

Internal Bus

Data

Serial Shift Register

I

2

C Data Buffer Register (IDBR)

I

2

C Control Register (ICR)

I

2

C Status Register (ISR)

I

2

C Slave Address Register (ISAR)

Address

Decode

I

2

C Bus

Monitor

SCL

Generator

SINT

SCL

SDA

ICLK

Internal Bus Interface