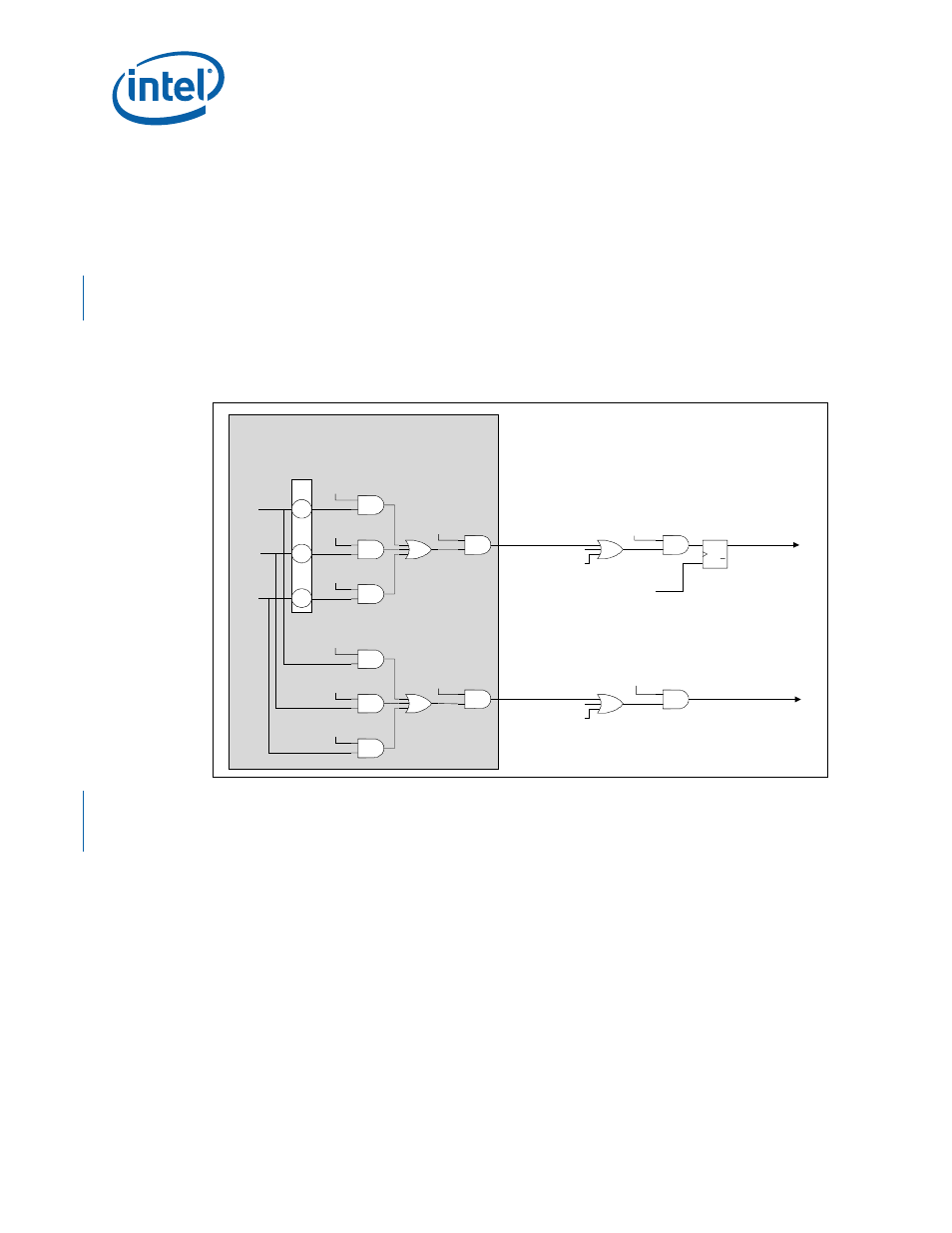

1 indicator output, Figure 118. indicator tree, 2 interrupt output – Intel CONTROLLERS 413808 User Manual

Page 744: 118 indicator tree, Pmon, Stat register and asserts the, Interrupt input to the interrupt control unit

Intel

®

413808 and 413812—PMON Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

744

Order Number: 317805-001US

16.5.2.1 Indicator Output

The

PMON

OUT pin is a shared indicator output pin. The resulting signal allows external

elements (OS, drivers, logic analyzer, etc.) to be aware of indicators without having to

rely on interrupts.

For 4138xx, the

PMON

OUT function is multiplexed onto the GPIO7 pin. When the

PMON

Indicator Output Enable bit is set in the

“PMON Feature Enable Register -

PMONEN”

, the

PMON

output function overrides the GPIO7 setting in the

15.2.1, “GPIO Output Enable Register — GPOE” on page 725

and

Output Data Register — GPOD” on page 728

.

Warning:

Since GPIO7 could be used for other purposes, care must be taken when enabling the

PMON

Indicator Output.

Note:

Indicator and Interrupt Enables are located in the

Global Indicator and Interrupt Enables are located in the

Register - PMONEN” on page 746

16.5.2.2 Interrupt Output

An internal interrupt is delivered to the Interrupt Control Unit when:

• Interrupts are enabled in the

“PMON Feature Enable Register - PMONEN”

(PMONEN[0]=1).

• One or more of the interrupt sources are enabled within the individual counter via

the indicator enable bits.

• The interrupt enable bit is set within the individual counter

• One or more of the enabled indicators is true

This sets the internal interrupt generated bit in the

PMON

STAT register and asserts the

PMON

interrupt input to the Interrupt control unit.

Figure 118. Indicator Tree

Status Register 0

+08H

Overflow

Underflow

Event

26

Command

Trigger

Event

25

Threshold

Event

24

OU Indicator

Enable

CT Indicator

Enable

TH Indicator

Enable

Counter 0

Counter 0

Counter 1

..

.

Counter 0

Counter 1

..

.

Interrupt

Indicator Output

Global Indicator

Output Enable

Global Interrupt

Enable

OU Indicator

Enable

CT Indicator

Enable

TH Indicator

Enable

Interrupt

Enable

Indicator Output

Enable

Indicator Output

( GPIO[7])

Interrupt

Q

Q

SET

CLR

S

R

Interrupt Status

Write-to-Clear

Enables located in

Command Register

+04H

Counter N

Counter N

B6320-01