2 tap controller, Figure 122. tap controller state diagram, 121 timing of actions in a tap controller state – Intel CONTROLLERS 413808 User Manual

Page 785: 122 tap controller state diagram, Test logic unit and testability—intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

785

Test Logic Unit and Testability—Intel

®

413808 and 413812

18.2.2

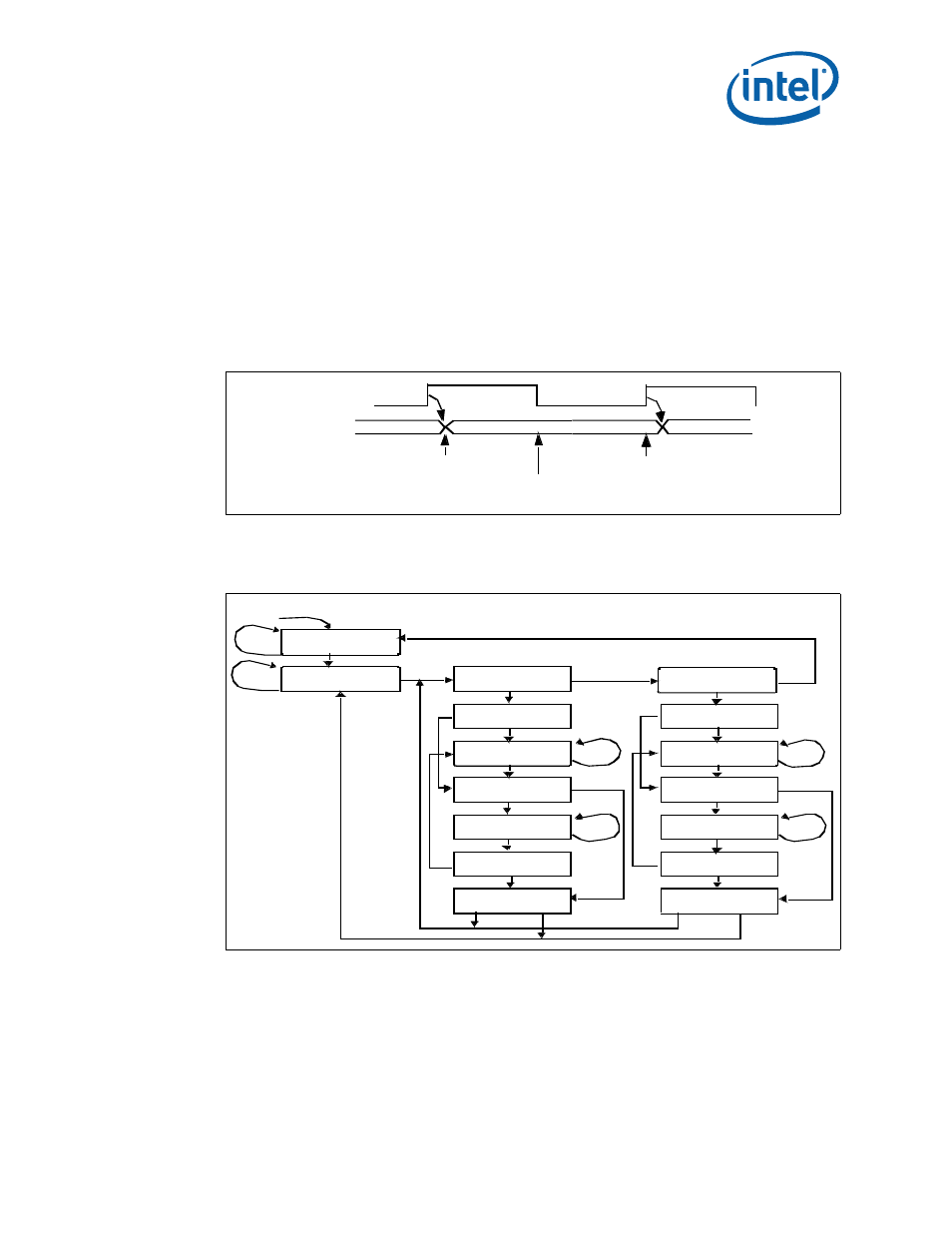

TAP Controller

, is a sixteen-state synchronous finite state

machine that changes state on the rising edge of

TCK

. The controller’s next state is

controlled by the state present at the

TMS

input. The TAP controller generates control

signals, which together with

TCK

and control signals decoded from the instruction

active in the instruction register, determine the operation of the test circuitry as defined

by the IEEE Standard.

All state transitions occur based on values of TMS on the rising edge of

TCK

Actions of

the test logic (instruction register, data registers, etc.) occur on either rising or falling

edge of

TCK

. See the description of each state to learn which.

For greater detail on the state machine and the public instructions, refer to IEEE

1149.1a Standard Test Access Port and Boundary-Scan Architecture Specification.

Figure 121. Timing of Actions in a TAP Controller State

TCK

Controller State

state entered

actions occurring on the rising edge

of TCK in the state occur here

actions occurring on the falling edge

of TCK in the state occur here

B6312-01

Figure 122. TAP Controller State Diagram

CAPTURE - IR

SHIFT - IR

EXIT1 - IR

PAUSE - IR

EXIT2 - IR

UPDATE - IR

SELECT-

IR - SCAN

CAPTURE - DR

SHIFT - DR

EXIT1 - DR

PAUSE - DR

EXIT2 - DR

UPDATE - DR

SELECT-

DR - SCAN

1

1

1

1

1

1

1

1

TEST - LOGIC -

RESET

RUN - TEST /

IDLE

1

1 *

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

* Note: State transitions occur based on the

value of TMS on rising edges of TCK

B6313-01