59 pci express device control register - pe_dctl, 59pci express device control register - pe_dctl, 199 pci express device control register - pe_dctl – Intel CONTROLLERS 413808 User Manual

Page 344: Pci express device control, Pci express, Section 3.17.59, “pci express, Register - pe_dctl, Express device control register - pe_dctl, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

344

Order Number: 317805-001US

3.17.59 PCI Express Device Control Register - PE_DCTL

This register controls various modes and features of ATU and Message Unit when

operating in the PCI Express mode.

Table 199. PCI Express Device Control Register - PE_DCTL (Sheet 1 of 2)

Bit

Default

Description

15

0

2

Preserved

14:12

010

2

Max_Read_Request_Size – This field sets the maximum Read Request size for the Device as a

Requester. The Device must not generate read requests with size exceeding the set value.

Defined encodings for this field are:

000b 128B max read request size

001b 256B max read request size

010b 512B max read request size

011b 1024B max read request size

100b 2048B max read request size

101b 4096B max read request size

110b Reserved

111b Reserved

Any reserved value is treated as 4096B.

Note:

In a multifunction configuration, the minimum programmed value from all functions is used

when issuing requests.

11

1

Enable No Snoop

10

0

Aux Power PM Enable - The ATU does not utilize Auxiliary power. Hard-wired to 0.

9

0

Phantom Functions Enable - 4138xx does not use phantom functions. Hard-wired to 0.

8

0

Extended Tag Field Enable - 4138xx does not generate 8 bit tags. Hard-wired to 0.

7:5

000

Max_Payload_Size – This field sets maximum TLP payload size for the device. As a receiver, the device

must handle TLPs as large as the set value; as transmitter, the device must not generate TLPs exceeding

the set value.

Defined encodings for this field are:

000b 128B max payload size

001b 256B max payload size

010b 512B max payload size

011b 1024B max payload size (Unsupported)

100b 2048B max payload size (Unsupported)

101b 4096B max payload size (Unsupported)

110b Reserved

111b Reserved

Any unsupported or reserved value is treated as 128B.

Note:

In a multifunction configuration, the minimum programmed value from all functions is used

when transmitting packets, and checking for max_payload violations.

4

1

Enable Relaxed Ordering

3

0

Unsupported Request Reporting Enable – This bit in conjunction with other bits controls the signaling of

Unsupported Requests by sending Error Messages. For a multi-function device, this bit controls error

reporting from the point-of-view of the respective function.

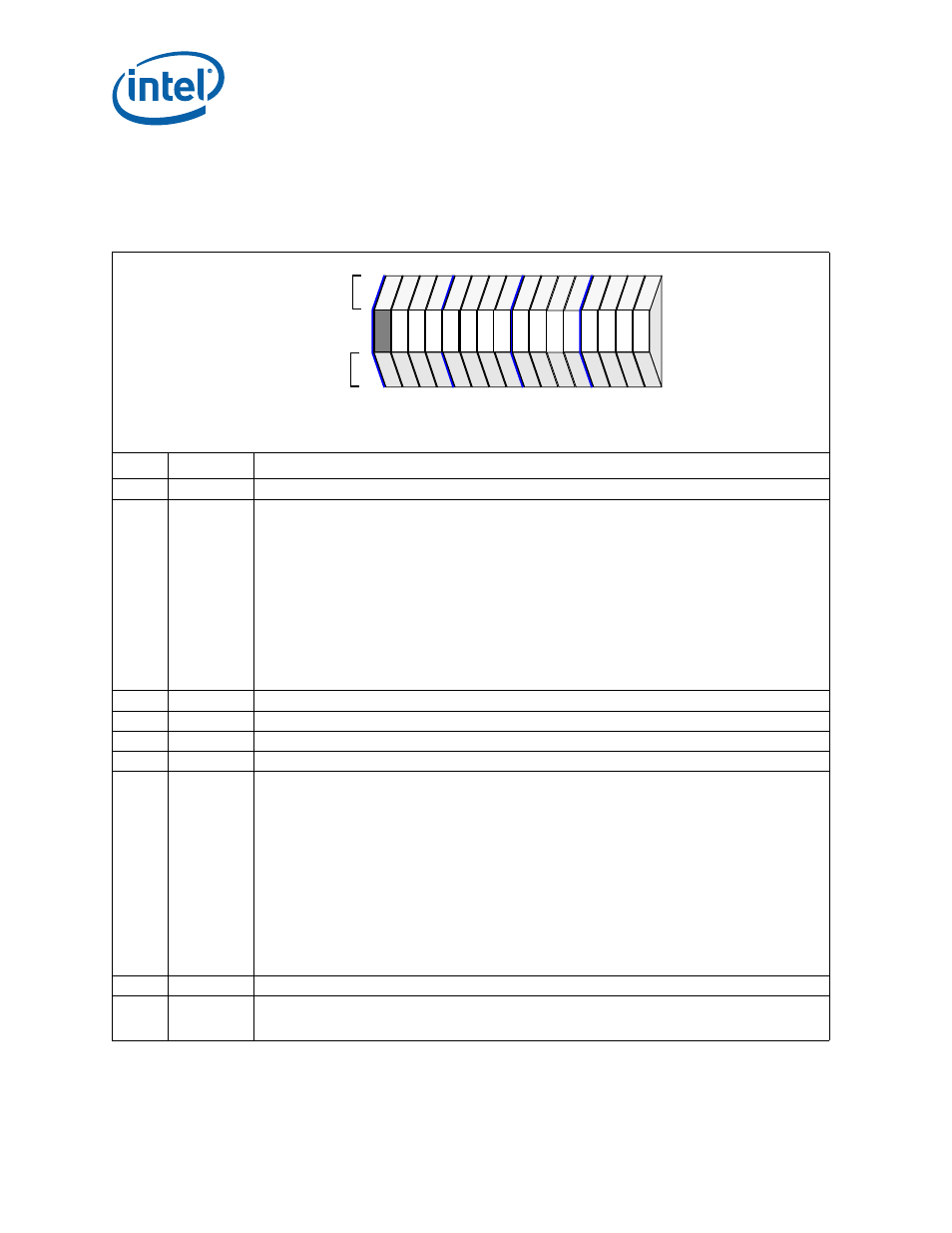

PCI

IOP

Attributes

Attributes

15

12

8

4

0

pr

pr

rw

rw

rw

rw

rw

rw

rw

rw

ro

ro

ro

ro

ro

ro

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0D8H