8 outbound interrupt mask register - oimr, Table 273. outbound interrupt mask register - oimr, 273 outbound interrupt mask register - oimr – Intel CONTROLLERS 413808 User Manual

Page 418: Intel, Bit default description

Intel

®

413808 and 413812—Messaging Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

418

Order Number: 317805-001US

4.7.8

Outbound Interrupt Mask Register - OIMR

The Outbound Interrupt Mask Register (OIMR) provides the ability to mask outbound

Host I/O Interface interrupts generated by the Messaging Unit. Each bit in the mask

register corresponds to a hardware interrupt bit in the Outbound Interrupt Status

Register. When the bit is set, the Host I/O Interface interrupt is not generated. When

the bit is clear, the interrupt is allowed to be generated.

Setting or clearing bits in this register does not affect the Outbound Interrupt Status

Register. They only affect the generation of the Host I/O Interface interrupt.

Table 273. Outbound Interrupt Mask Register - OIMR

Bit

Default

Description

31

0

2

Firmware Interrupt Mask - When set, this bit masks the Firmware Reset interrupt signal when the

Firmware interrupt bit in the Outbound Reset Control and Status Register is set.

30:05

000000H Reserved

07

0

2

PCI Interrupt D Mask - When set, this bit masks the PCI Interrupt D signal when the PCI Interrupt D bit

in the in the Outbound Doorbell Register is set.

06

0

2

PCI Interrupt C Mask - When set, this bit masks the PCI Interrupt C signal when the PCI Interrupt C bit

in the in the Outbound Doorbell Register is set.

05

0

2

PCI Interrupt B Mask - When set, this bit masks the PCI Interrupt B signal when the PCI Interrupt B bit

in the in the Outbound Doorbell Register is set.

04

0

2

PCI Interrupt A Mask - When set, this bit masks the PCI Interrupt A signal when the PCI Interrupt A bit

in the in the Outbound Doorbell Register is set.

03

0

2

Outbound Post Queue Interrupt Mask - When set, this bit masks the PCI interrupt generated when data

in the prefetch buffer is valid.

02

0

2

Outbound Doorbell Interrupt Mask - When set, this bit masks the Software Interrupt generated by the

Outbound Doorbell Register.

01

0

2

Outbound Message 1 Interrupt Mask - When set, this bit masks the Outbound Message 1 Interrupt

generated by a write to the Outbound Message 1 Register.

00

0

2

Outbound Message 0 Interrupt Mask- When set, this bit masks the Outbound Message 0 Interrupt

generated by a write to the Outbound Message 0 Register.

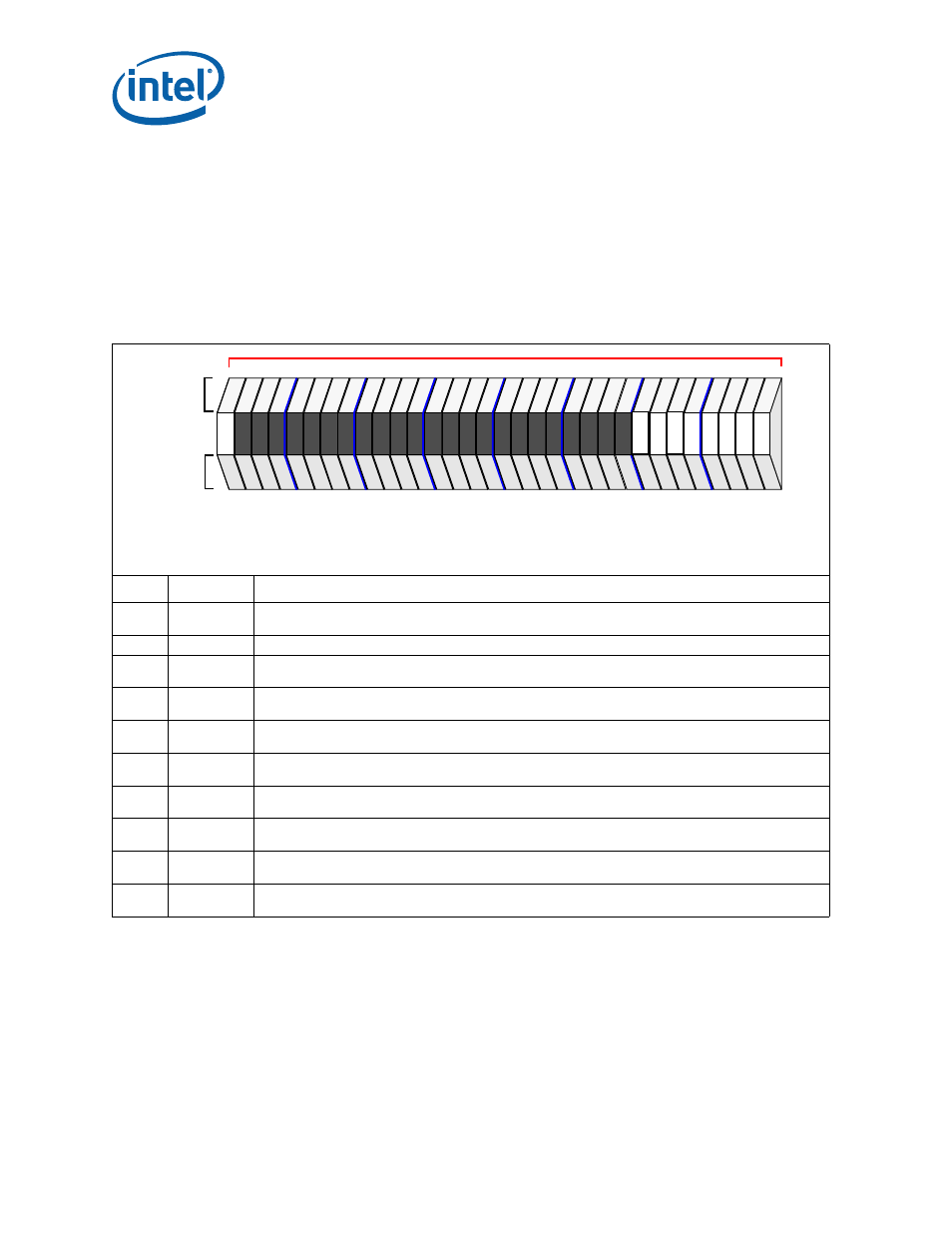

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

MU/PCI Base Address Offset

OIMR: 0034H

internal bus address offset

OIMR: 4034H