Table 377. interrupt input pin descriptions, 377 interrupt input pin descriptions – Intel CONTROLLERS 413808 User Manual

Page 570

Intel

®

413808 and 413812—Interrupt Controller Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

570

Order Number: 317805-001US

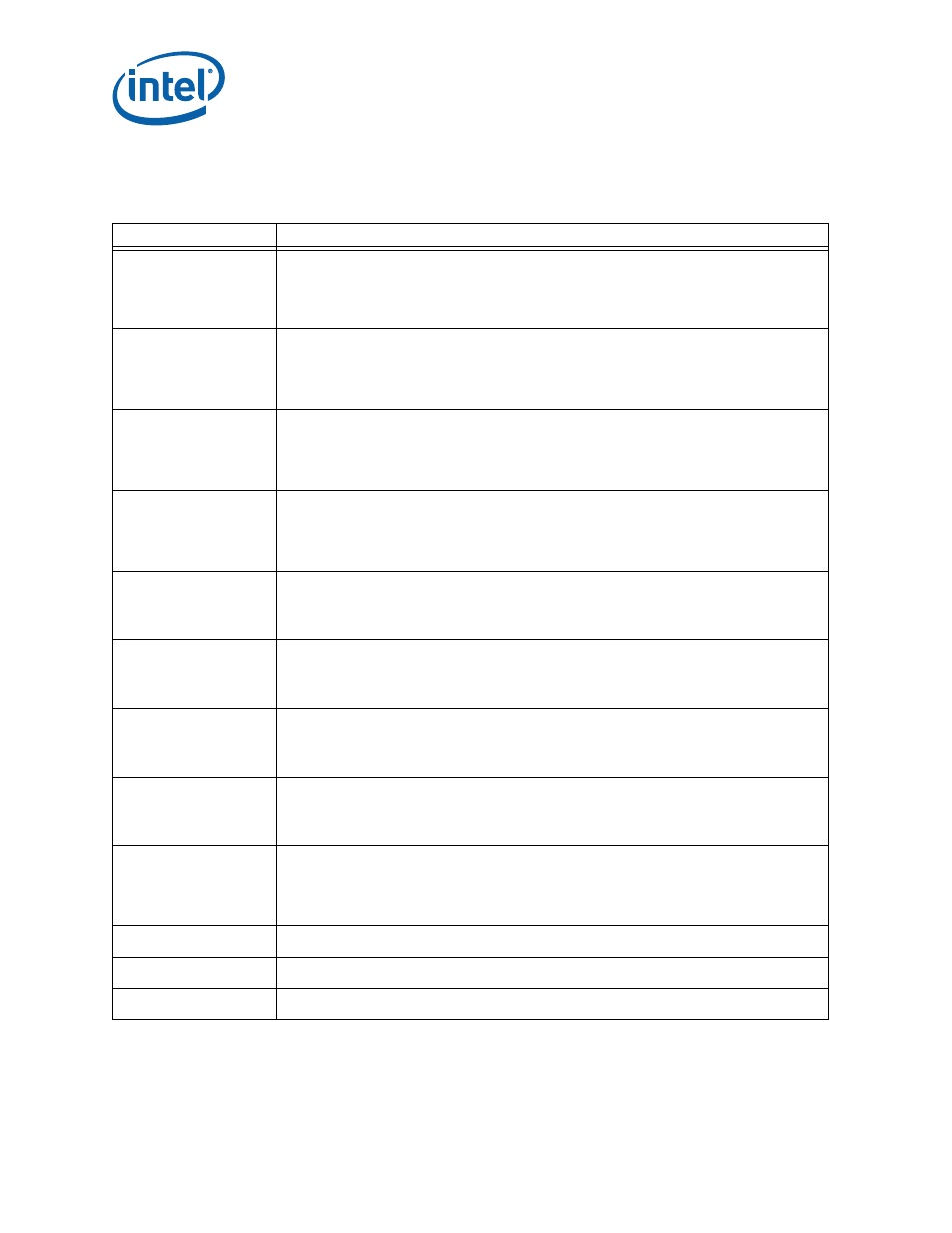

The external interrupt input interface for the 4138xx consists of the pins shown in

Table 377. Interrupt Input Pin Descriptions

Signal

Description

P_INTA#

/

XINT0#

/

GPIO[8]

This is a bi-directional pin. When 4138xx is setup as an endpoint with the PCI-X interface, this pin

acts as an output pin (

P_INTA#

). This pin can act as an input (

XINT0#

) and drive the

XINT0#

input of the Interrupt Controller. The

Interrupt Controller Unit input

XINT0#

can be steered to

either the FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given

pin as an interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can

also function as a general purpose input/output pin (

GPIO[8]

) when not used as an interrupt pin.

P_INTB#

/

XINT1#

/

GPIO[9]

This is a bi-directional pin. When 4138xx is setup as an endpoint with the PCI-X interface, this pin

acts as an output pin (

P_INTB#

). This pin can act as an input (

XINT1#

) and drive the

XINT1#

input of the Interrupt Controller. The

Interrupt Controller Unit input

XINT1#

can be steered to

either the FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given

pin as an interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can

also function as a general purpose input/output pin (

GPIO[9]

) when not used as an interrupt pin.

P_INTC#

/

XINT2#

/

GPIO[10]

This is a bi-directional pin. When 4138xx is setup as an endpoint with the PCI-X interface, this pin

acts as an output pin (

P_INTC#

). This pin can act as an input (

XINT2#

) and drive the

XINT2#

input of the Interrupt Controller. The

Interrupt Controller Unit input

XINT2#

can be steered to

either the FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given

pin as an interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can

also function as a general purpose input/output pin (

GPIO[10]

) when not used as an interrupt pin.

P_INTD#

/

XINT3#

/

GPIO[11]

This is a bi-directional pin. When 4138xx is setup as an endpoint with the PCI-X interface, this pin

acts as an output pin (

P_INTD#

). This pin can act as an input (

XINT3#

) and drive the

XINT3#

input of the Interrupt Controller. The

Interrupt Controller Unit input

XINT3#

can be steered to

either the FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given

pin as an interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can

also function as a general purpose input/output pin (

GPIO[11]

) when not used as an interrupt pin.

XINT4#

/

GPIO[12]

This is a bi-directional pin. This pin can act as an input (

XINT4#

) and drive the

XINT4#

input of

the Interrupt Controller. The

Interrupt Controller Unit input

XINT4#

can be steered to either the

FIQ or the FIQ internal interrupt input of the Intel XScale

®

processor. To enable a given pin as an

interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can also

function as a general purpose input/output pin (

GPIO[12]

) when not used as an interrupt pin.

XINT5#

/

GPIO[13]

This is a bi-directional pin. This pin can act as an input (

XINT5#

) and drive the

XINT5#

input of

the Interrupt Controller. The

Interrupt Controller Unit input

XINT5#

can be steered to either the

FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given pin as an

interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can also

function as a general purpose input/output pin (

GPIO[13]

) when not used as an interrupt pin.

XINT6#

/

GPIO[14]

This is a bi-directional pin. This pin can act as an input (

XINT6#

) and drives the

XINT6#

input of

the Interrupt Controller. The

Interrupt Controller Unit input

XINT6#

can be steered to either the

FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given pin as an

interrupt into the ICU, it needs to be unmasked in the INTCTL1 register. This pin can also function

as a general purpose input/output pin (

GPIO[14]

) when not used as an interrupt pin.

XINT7#

/

GPIO[15]

This is a bi-directional pin. This pin can act as an input (

XINT7#

) and drives the

XINT7#

input of

the Interrupt Controller. The

Interrupt Controller Unit input

XINT7#

can be steered to either the

FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor. To enable a given pin as an

interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0] register. This pin can also

function as a general purpose input/output pin (

GPIO[15]

) when not used as an interrupt pin.

XINT[15:8]#

/

GPIO[7:0]

These are bi-directional pins. These pins can act as inputs (

XINT[15:8]#

) and drive the

XINT[15:8]#

input of the Interrupt Controller. The

Interrupt Controller Unit input

XINT[15:8]#

can be steered to either the FIQ or the IRQ internal interrupt input of the Intel XScale

®

processor.

To enable a given pin as an interrupt into the ICU, it needs to be unmasked in the INTCTL[3:0]

register. These pins can also function as general purpose input/output pins (

GPIO[7:0]

) when not

used as an interrupt pin.

HPI#

HPI#

input can be enabled/disabled by the INTCTL[3:0] register, but can be steered to either the

FIQ or the IRQ internal interrupt.

NMI0#

NMI0#

input is a non-maskable falling edge triggered signal and is internally synchronized and

directly driven to Intel XScale

®

processor

0.

NMI1#

NMI1#

input is a non-maskable falling edge triggered signal and is internally synchronized and

directly driven to Intel XScale

®

processor

1.