2 outbound queues, Table 12. outbound queues, 12 outbound queues – Intel CONTROLLERS 413808 User Manual

Page 86: Section 2.6.2

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

86

Order Number: 317805-001US

2.6.2

Outbound Queues

The outbound queues of the ATU are used to hold read and write transactions from the

core processor directed at the PCI bus. Each ATU outbound queue structure has a

separate read queue, write queue, and address queue.

contains information

about ATU outbound queues.

The outbound queues are capable of holding outbound memory read, memory write,

I/O read, and I/O write transactions. The type of transaction used is defined by the

internal bus address and the command used on the internal bus. See

and

for details on outbound address translation.

When an internal bus agent initiates an outbound write transaction, the address is

entered into the OWADQ (when not full). The data from the internal bus write is then

entered into the OWQ and the transaction is forwarded to the PCI bus. When the write

completes (or an error occurs), the address is flushed from the OWADQ. Data is flushed

only for the master abort or target abort cases.

For outbound reads, the address is entered into the OTQ (when not full) and a split

response termination is signaled to the requester on the internal bus. Read data is

fetched and returned to the requester on the internal bus.

2.6.2.1

Relaxed Ordering and No Snoop Outbound Request Attributes

In PCI-X mode, the ATU may set the Relaxed Ordering (RO) bit 29 of the Requester

Attributes and/or the No Snoop (NS) bit 30 of the Requester Attributes for an outbound

request.

For any other outbound requests, the NS and RO attribute bits are set to 0.

Note:

The PCI-X Protocol Addendum to the PCI Local Bus Specification, Revision 2.0 permits

the ATU to set the RO bit to ‘1’ in the Requester Attributes only when enabled by bit 1

of the

“PCI-X Command Register - PCIXCMD” on page 191

.

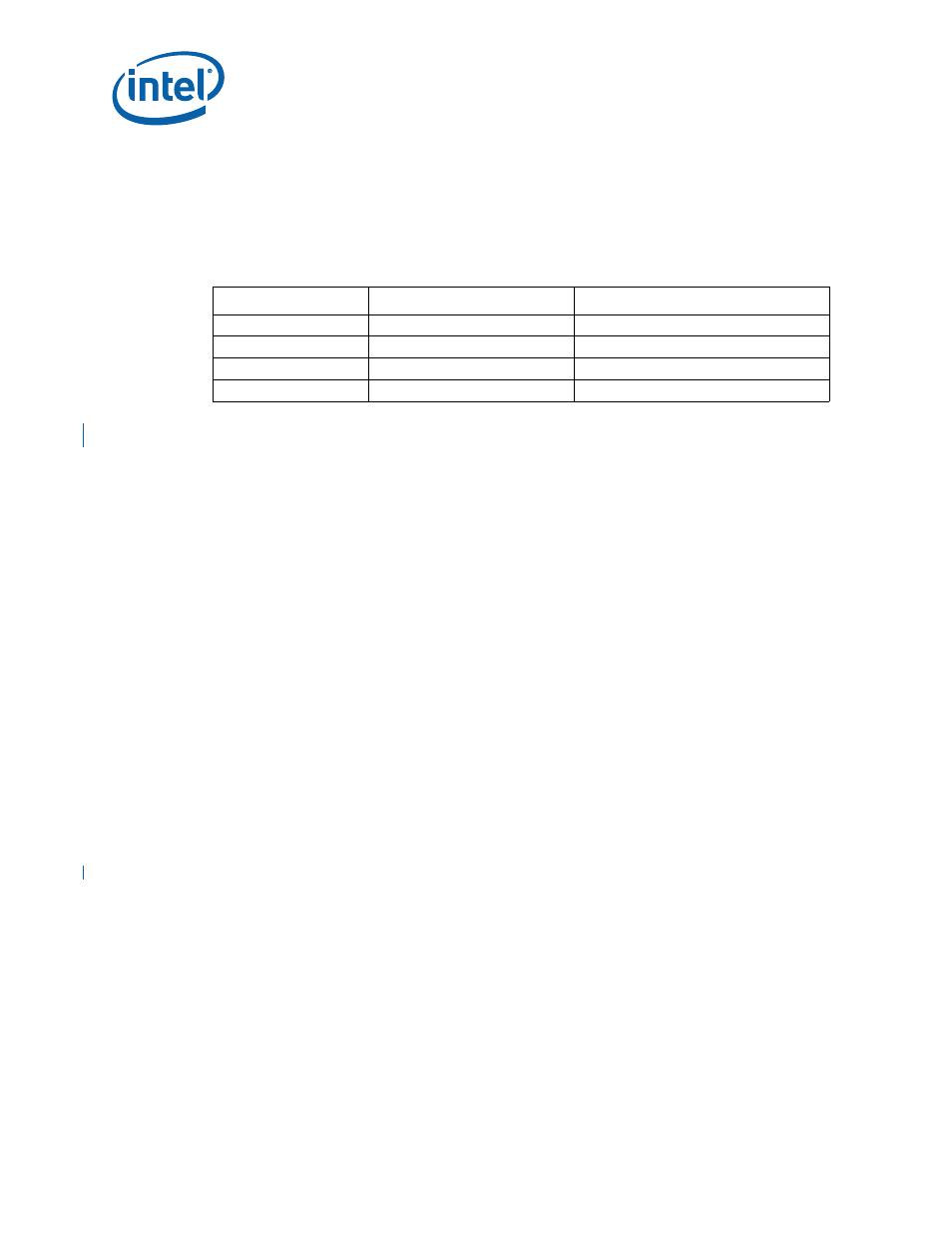

Table 12. Outbound Queues

Queue Mnemonic

Queue Name

Queue Size (Bytes)

OWQ

Outbound Write Data Queue

4 KBytes (4*1024B)

OWADQ

Outbound Write Address Queue

4 Transaction Addresses

ORQ

Outbound Read Data Queue

2 or 4 KBytes (4* 512B or 4*1024B)

a

a. The ORQ can be throttled between 2 Kbytes or 4 Kbytes depending on the setting of the Maximum Memory

Read Byte Count (MMRBC) field of the PCI-X Command register (see

Section 2.14.55, “PCI-X Command

Register - PCIXCMD” on page 191

). When the MMRBC is set to 512 bytes (default value), the ORQ is only

capable of handling 2 Kbytes of SRC data, otherwise, the ORQ handles 4 Kbytes of SRC data.

OTQ

Outbound Transaction Queue

8 Addresses/Commands