62 pci express link control register - pe_lctl, 62pci express link control register - pe_lctl, 202 pci express link control register pe_lctl – Intel CONTROLLERS 413808 User Manual

Page 348: Pci express link control register, Pe_lctl, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

348

Order Number: 317805-001US

3.17.62 PCI Express Link Control Register - PE_LCTL

This register controls various modes and features of ATU and Message Unit when

operating in the PCI Express mode.

Table 202. PCI Express Link Control Register PE_LCTL

Bit

Default

Description

15:8

00

2

Preserved

7

0

Extended Synch - This bit when set forces the transmission of 4096 FTS ordered sets in the L0s state

followed by a single SKP ordered set prior to entering the L0 state, and the transmission of 1024 TS1

ordered sets in the L1 state prior to entering the Recovery state. This mode provides external devices

(e.g., logic analyzers) monitoring the Link time to achieve bit and Symbol lock before the Link enters the

L0 or Recovery states and resumes communication.

6

0

Common Clock Configuration - When set indicates that this component and the component at the

opposite end of this Link are operating with a distributed common reference clock.

This bit used to report the correct L0s and L1 Exit Latencies in the PCIE_LCAP register

5

0

Retrain Link -

As an end point, this bit is hard-wired to 0

As a root complex, this bit initiates Link Retraining when set.

This bit is self clearing and always returns 0 when read.

4

0

Link Disable -

As and endpoint, this bit is hard-wired to 0

As a root complex, this bit disables the Link when set to 1b.

Writes to this bit are immediately reflected in the value read from the bit, regardless of actual Link state.

3

Endpoint: 0

Root

Complex:1

Read Completion Boundary (RCB) Control - Indicates the Root Complex’s RCB.

As an end point, this field is not supported and is hard-wired to 0.

For Root Complex, Hard-wired to 1b indicting 128Byte RCB

2

0

Reserved

1:0

00

Active State PM Control - This field controls the level of active state PM supported on the given PCI

Express Link.

PCI

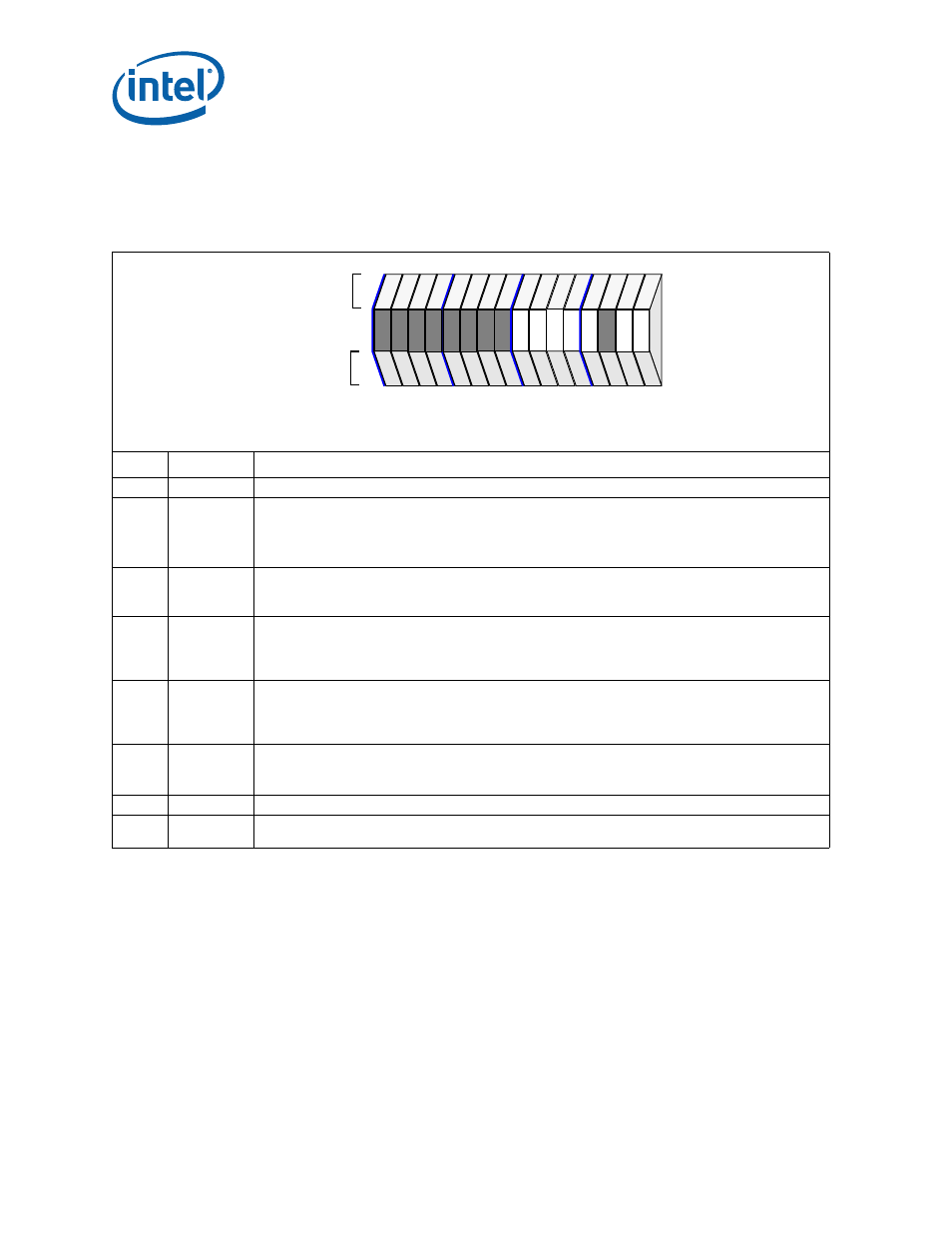

IOP

Attributes

Attributes

15

12

8

4

0

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

pr

rw

rw

rw

rw

rw

rw

rw

rw

ro

ro

pr

pr

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0E0H