119 supported address spaces and transaction types – Intel CONTROLLERS 413808 User Manual

Page 235

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

235

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

The ATU unit allows for recognition and generation of multiple PCI Express Transaction

Layer Packets (TLP) types.

shows the commands supported for both inbound

and outbound ATU transactions. The type of operation seen by the ATU on inbound

transactions are determined by the PCI Express requester who initiates the transaction.

Claiming an inbound transaction depends on the address range programmed within the

inbound translation window. The type of transaction used by the ATU on outbound

transactions generated by the core processor is determined by the internal bus address

and the fixed outbound windowing scheme.

ATU supports all four address spaces defined within the PCI Express architecture as

both a requester and completer. These address spaces and corresponding transaction

types are detailed in

.

ATU does not support Locked Requests as a Completer nor generate them as a

Requestor.

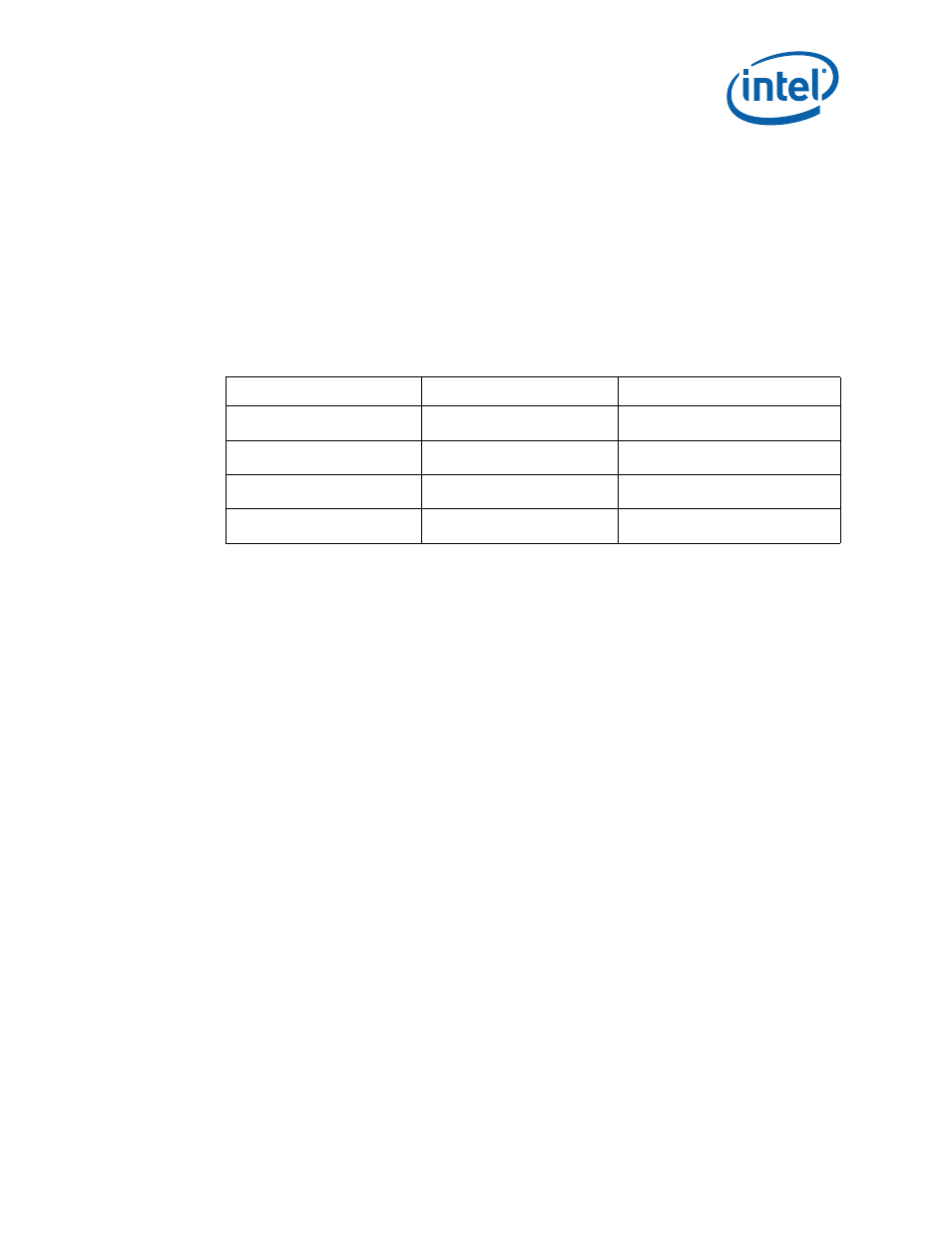

Table 119. Supported Address Spaces and Transaction Types

Address Space

Transaction Type

Basic Usage

Memory

a

a. ATU supports both 32-bit and 64-bit addressing for Memory space transactions.

Read

Write

Transfer data to/from a

memory-mapped location

I/O

Read

Write

Transfer data to/from and

I/O-mapped location

Configuration

Read

Write

Device configurations/setup

Message

Baseline

Vendor-defined

From event signalling mechanism to

general purpose messaging