Intel CONTROLLERS 413808 User Manual

Page 813

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

813

Peripheral Registers—Intel

®

413808 and 413812

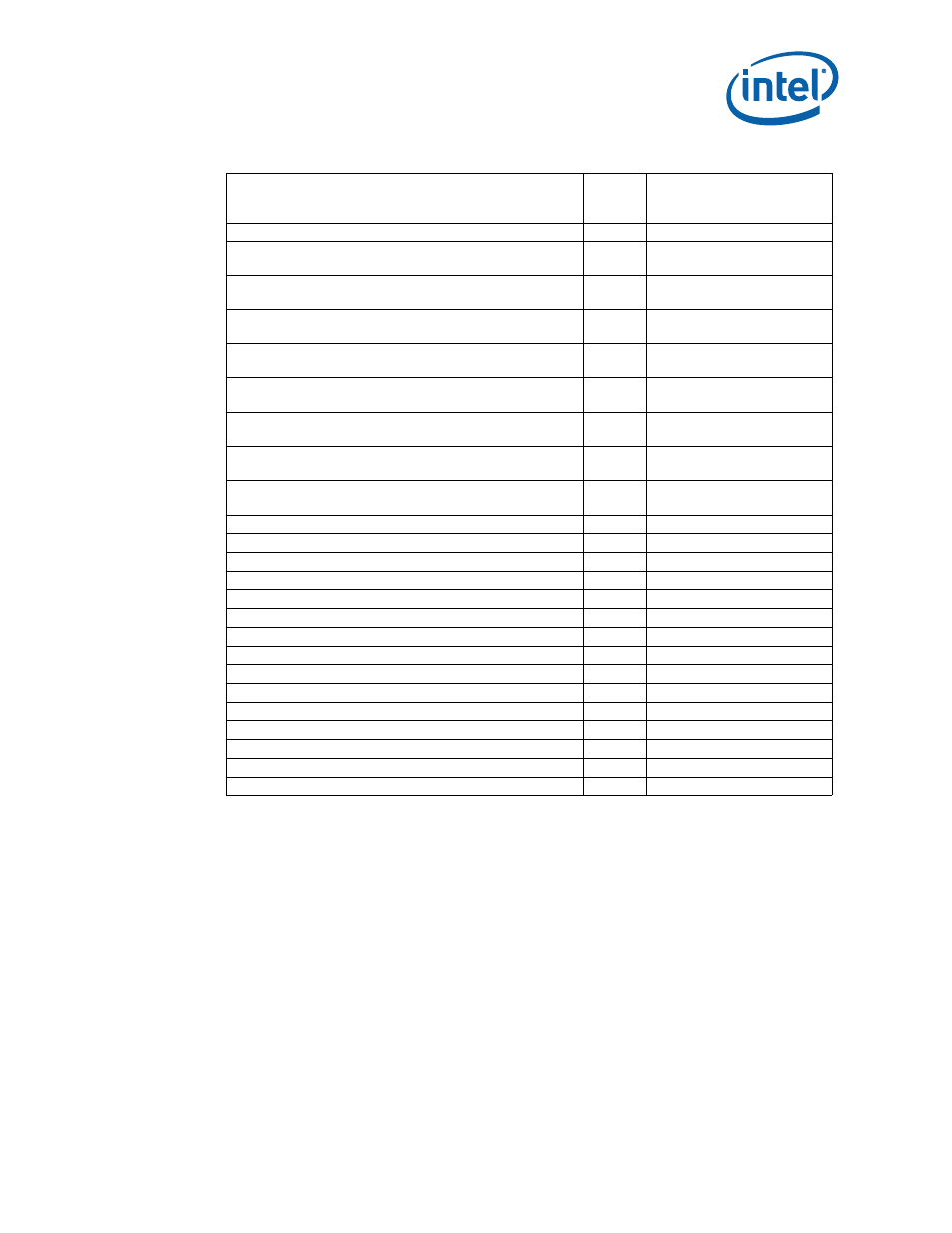

Outbound I/O Window Translate Value Register — OIOWTVR

32

+304H

Outbound Upper Memory Window Base Address Register 0

- OUMBAR0

32

+308H

Outbound Upper 32-bit Memory Window Translate Value

Register 0 — OUMWTVR0

32

+30CH

Outbound Upper Memory Window Base Address Register 1

- OUMBAR1

32

+310H

Outbound Upper 32-bit Memory Window Translate Value

Register 1 — OUMWTVR1

32

+314H

Outbound Upper Memory Window Base Address Register 2

- OUMBAR2

32

+318H

Outbound Upper 32-bit Memory Window Translate Value

Register 2 — OUMWTVR2

32

+31CH

Outbound Upper Memory Window Base Address Register 3

- OUMBAR3

32

+320H

Outbound Upper 32-bit Memory Window Translate Value

Register 3 — OUMWTVR3

32

+324H

Reserved.

32

+328H

Reserved.

32

+32CH

Outbound Configuration Cycle Address Register — OCCAR

32

+330H

Outbound Configuration Cycle Data Register — OCCDR

32

+334H

Outbound Configuration Cycle Function Number — OCCFN

32

+338H

Reserved

x

+33CH through +37FH

PCI Interface Error Control and Status Register — PIECSR

32

+380H

PCI Interface Error Address Register — PCIEAR

32

+384H

PCI Interface Error Upper Address Register — PCIEUAR

32

+388H

PCI Interface Error Context Address Register — PCIECAR

32

+38CH

Reserved

x

+390H

Internal Arbiter Control Register — IACR

16

+394H

Reserved

x

+396H

Multi-Transaction Timer — MTT

8

+398H

Reserved

x

+39CH through +FFFH

Table 544. Address Translation Unit Registers — ATUX (Sheet 3 of 3)

Register Description (Name)

Register

Size in

Bits

Internal Bus Address Offset

(Relative to ATUX Base

Address Offset)

Notes:

1.

MSI and MSI-X Capability Registers are documented in the Messaging Unit Chapter.