5 uart 0-1, Table 532. uart 0-1 offset, Table 533. uart – Intel CONTROLLERS 413808 User Manual

Page 804: 532 uart 0-1 offset, 533 uart, Uart

Intel

®

413808 and 413812—Peripheral Registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

804

Order Number: 317805-001US

19.6.1.5 UART 0-1

The 4138xx contains two instances of the UART. Each UART is allocated 64Bytes of

PMMR registers space that is located at the offset specified in

which is

relative to the PMMRBAR.

Use the following equation to calculate the actual register address:

Internal Bus Address = PMMRBAR + UART Base Address Offset + Register Offset.

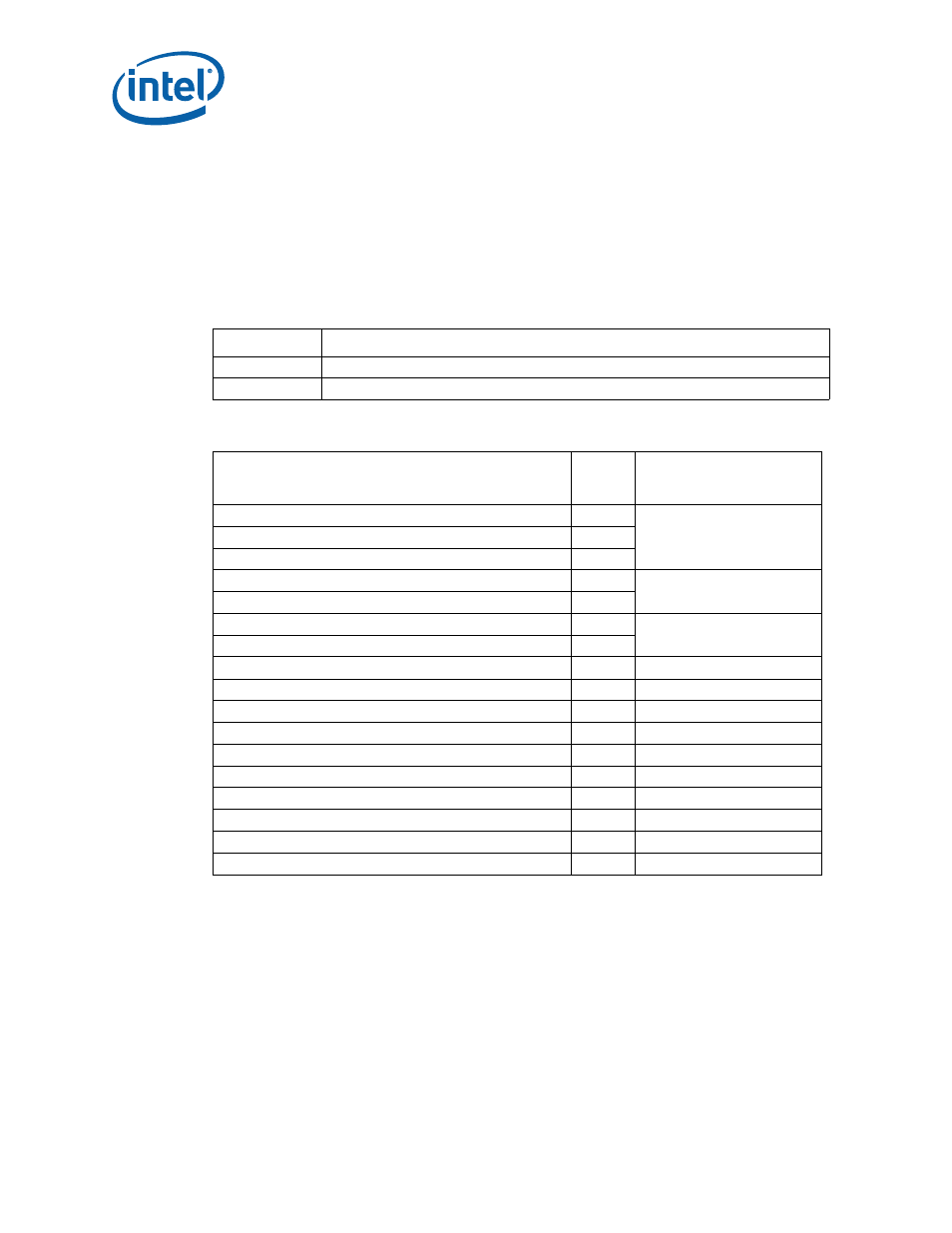

Table 532. UART 0-1 Offset.

Unit

UARTx Base Address Offset (Relative to PMMRBAR)

UART 0

+2300H

UART 1

+2340H

Table 533. UART

Register Description (Name)

Register

Size in

Bits

Internal Bus Address Offset

(Relative to UARTx Base

Address Offset)

UART x Receive Buffer Register (Read Only) (DLAB=0)

32

+00H

UART x Transmit Holding Register (Write Only) (DLAB=0)

32

UART x baud Divisor Latch Low byte (DLAB=1)

8

UART x Interrupt Enable Register (DLAB=0)

8

+04H

UART x baud Divisor Latch High byte (DLAB=1)

8

UART x Interrupt ID Register (Read Only)

8

+08H

UART x FIFO Control Register (Write Only)

8

UART x Line Control Register

8

+0CH

UART x Modem Control Register

8

+10H

UART x Line Status Register

8

+14H

UART x Modem Status Register

8

+18H

UART x Scratch Pad Register

8

+1CH

Reserved

32

+20H

UART x FIFO Occupancy Register

8

+24H

UART x Autobaud Control Register

8

+28H

UART x Autobaud Count Register

16

+2CH

Reserved

+30H through +3FH