141 atu pci configuration register space, Table 141 – Intel CONTROLLERS 413808 User Manual

Page 294

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

294

Order Number: 317805-001US

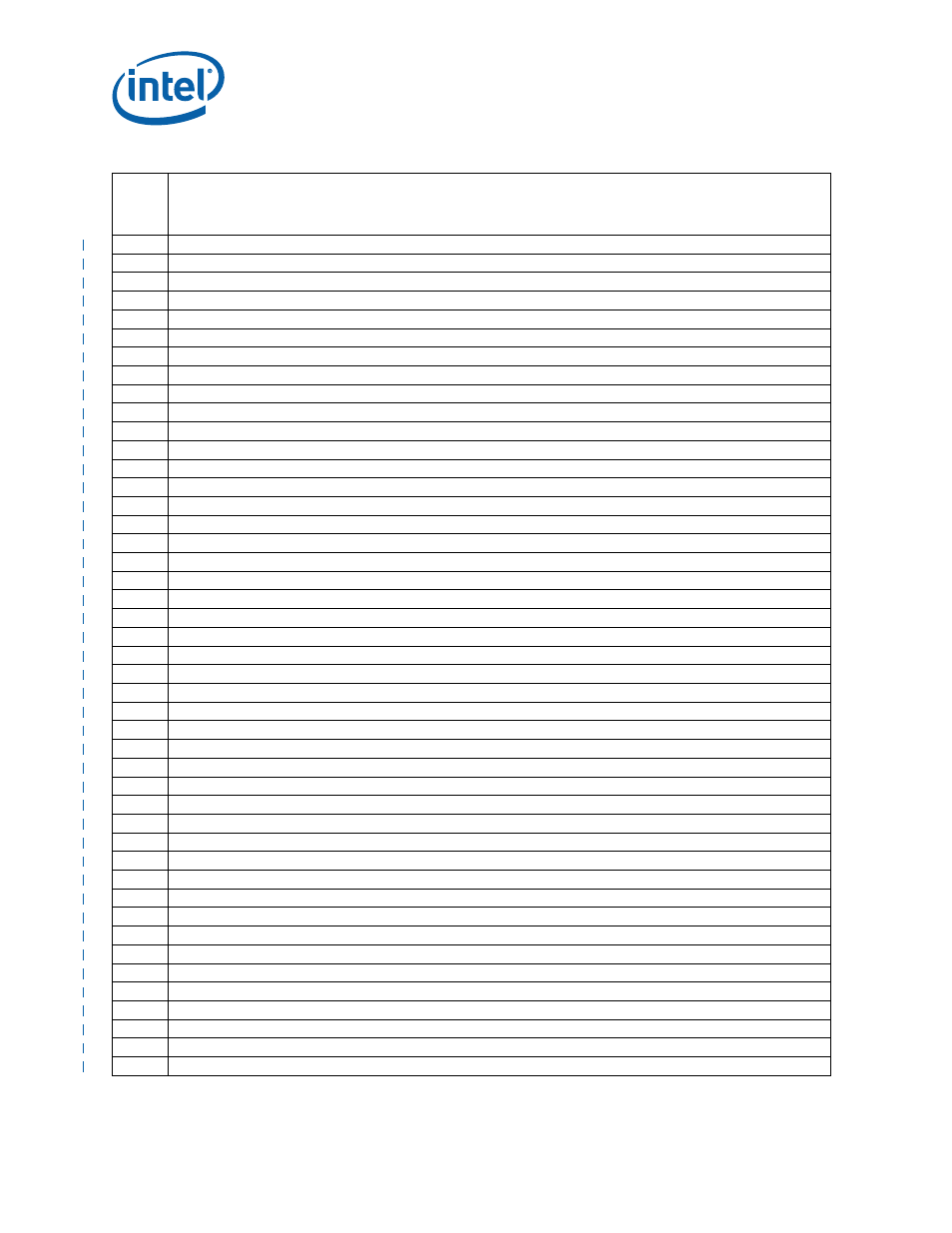

Table 141. ATU PCI Configuration Register Space (Sheet 1 of 3)

Interna

l Bus

Address

Offset

ATU PCI Configuration Register Section, Name, Page

+000H

Section 3.17.3, “ATU Vendor ID Register - ATUVID” on page 297

+002H

Section 3.17.4, “ATU Device ID Register - ATUDID” on page 297

+004H

Section 3.17.5, “ATU Command Register - ATUCMD” on page 298

+006H

Section 3.17.6, “ATU Status Register - ATUSR” on page 299

+008H

Section 3.17.7, “ATU Revision ID Register - ATURID” on page 300

+009H

Section 3.17.8, “ATU Class Code Register - ATUCCR” on page 300

+00CH

Section 3.17.9, “ATU Cacheline Size Register - ATUCLSR” on page 301

+00DH

Section 3.17.10, “ATU Latency Timer Register - ATULT” on page 301

+00EH

Section 3.17.11, “ATU Header Type Register - ATUHTR” on page 302

+00FH

Section 3.17.12, “ATU BIST Register - ATUBISTR” on page 303

+010H

Section 3.17.13, “Inbound ATU Base Address Register 0 - IABAR0” on page 304

+014H

Section 3.17.14, “Inbound ATU Upper Base Address Register 0 - IAUBAR0” on page 305

+018H

Section 3.17.16, “Inbound ATU Base Address Register 1 - IABAR1” on page 308

+01CH

Section 3.17.17, “Inbound ATU Upper Base Address Register 1 - IAUBAR1” on page 309

+020H

Section 3.17.18, “Inbound ATU Base Address Register 2 - IABAR2” on page 310

+024H

Section 3.17.19, “Inbound ATU Upper Base Address Register 2 - IAUBAR2” on page 311

+02CH

Section 3.17.20, “ATU Subsystem Vendor ID Register - ASVIR” on page 312

+02EH

Section 3.17.21, “ATU Subsystem ID Register - ASIR” on page 312

+030H

Section 3.17.22, “Expansion ROM Base Address Register - ERBAR” on page 313

+034H

Section 3.17.23, “ATU Capabilities Pointer Register - ATU_Cap_Ptr” on page 314

+03CH

Section 3.17.24, “ATU Interrupt Line Register - ATUILR” on page 315

+03DH

Section 3.17.25, “ATU Interrupt Pin Register - ATUIPR” on page 316

+03EH

Section 3.17.26, “ATU Minimum Grant Register - ATUMGNT” on page 316

+03FH

Section 3.17.27, “ATU Maximum Latency Register - ATUMLAT” on page 317

+040H

Section 3.17.28, “Inbound ATU Limit Register 0 - IALR0” on page 318

+044H

Section 3.17.29, “Inbound ATU Translate Value Register 0 - IATVR0” on page 319

+048H

Section 3.17.30, “Inbound ATU Upper Translate Value Register 0 - IAUTVR0” on page 319

+04CH

Section 3.17.31, “Inbound ATU Limit Register 1 - IALR1” on page 320

+050H

Section 3.17.32, “Inbound ATU Translate Value Register 1 - IATVR1” on page 321

+054H

Section 3.17.33, “Inbound ATU Upper Translate Value Register 1 - IAUTVR1” on page 321

+058H

Section 3.17.34, “Inbound ATU Limit Register 2 - IALR2” on page 322

+05CH

Section 3.17.35, “Inbound ATU Translate Value Register 2 - IATVR2” on page 323

+060H

Section 3.17.36, “Inbound ATU Upper Translate Value Register 2 - IAUTVR2” on page 324

+064H

Section 3.17.37, “Expansion ROM Limit Register - ERLR” on page 324

+068H

Section 3.17.38, “Expansion ROM Translate Value Register - ERTVR” on page 325

+06CH

Section 3.17.39, “Expansion ROM Upper Translate Value Register - ERUTVR” on page 325

+070H

Section 3.17.40, “ATU Configuration Register - ATUCR” on page 326

+074H

Section 3.17.41, “PCI Configuration and Status Register - PCSR” on page 327

+078H

Section 3.17.42, “ATU Interrupt Status Register - ATUISR” on page 329

+07CH

Section 3.17.43, “ATU Interrupt Mask Register - ATUIMR” on page 332

+080H

Section 3.17.44, “PCI Express Message Control/Status Register - PEMCSR” on page 333

+084H

Section 3.17.45, “PCI Express Link Control/Status Register - PELCSR” on page 334

+090H

Section 3.17.46, “VPD Capability Identifier Register - VPD_Cap_ID” on page 335

+091H

Section 3.17.47, “VPD Next Item Pointer Register - VPD_Next_Item_Ptr” on page 335

+092H