1 pmon command register 0-7 - pmon_cmd[0:7, Pmon command register 0-7, Pmon – Intel CONTROLLERS 413808 User Manual

Page 749: This 32-bit register allows control of the, Pmon unit—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

749

PMON Unit—Intel

®

413808 and 413812

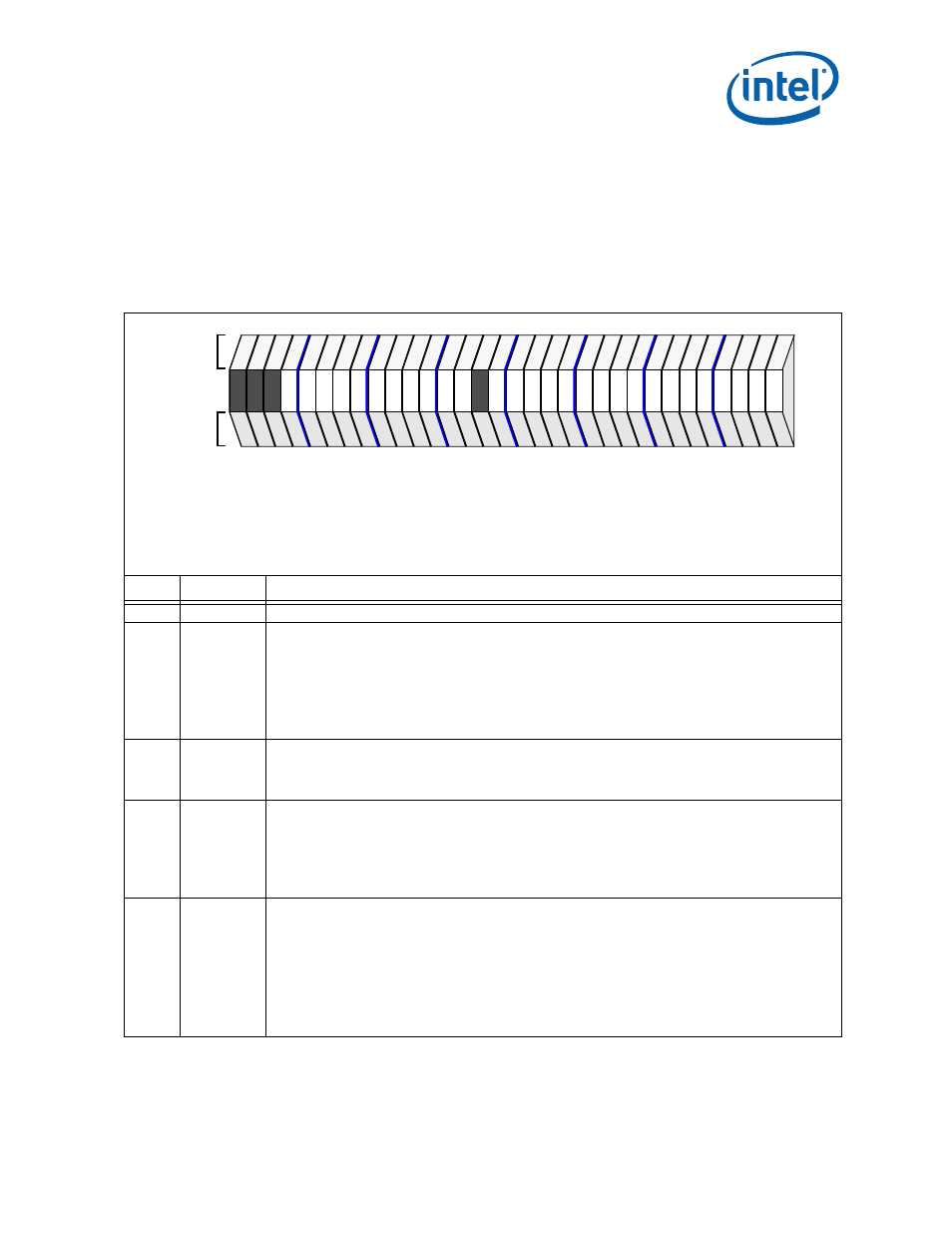

16.5.6.1 PMON Command Register 0-7 - PMON_CMD[0:7]

This 32-bit register allows control of the

PMON

counter. When this register is written,

the previous register contents are overwritten. All 32 bits must be programmed each

time the register is written. When the register contained a command that was still

waiting to be triggered, it would be flushed without ever being executed. The currently

executing command continues to be executed only until the newly programmed

command is triggered to execute.

Table 492. PMON Command Register 0-7 - PMON_CMD[0:7] (Sheet 1 of 4)

Bit

Default

Description

31:29

00b

Reserved

28

0b

Interrupt Enable

This bit causes the counter to set the global interrupt generated bit in the

PMON

STAT register.

0 = An interrupt is not generated from this counter

1 = The global interrupt generated bit is set when one or more of the Overflow/Underflow, Command

Trigger, and Threshold status bits are asserted and the individual indicator enable(s) are set. An

interrupt is delivered when there is not an existing interrupt being processed from

PMON

.

Upon servicing the Interrupt, the status registers should be cleared by software so that another

Interrupt is not sent.

27

0b

Indicator Output Enable:

0 =

PMON

OUT is not asserted when the indicators are valid.

1 = The

PMON

OUT signal is asserted when the conditions enabled via the indicator enable bits are

true.

26

0b

Overflow/Underflow Indicator Enable (OUIE)

0 = No indication provided when a counter overflow or underflow occurs except for setting the

Overflow/Underflow Indicator (OUI) status bit.

1 = When the overflow/underflow condition is true, the counter sets the status bit and possibly assert

the

PMON

OUT pin or enable the generation of an interrupt. This is controlled by the

PMON

OUT

Enable and Interrupt Enable respectively. Interrupts are driven directly off of the status bits,

whereas the

PMON

OUT pin is driven directly from the condition.

25

0b

Command Trigger Indicator Enable (CTIE)

0 = No indication provided when a command is triggered except for setting the Command Trigger

Indicator (CTI) status bit.

1 = When the command trigger condition is true, the counter sets the status bit and possibly assert the

PMON

OUT pin or enable the generation of an interrupt. This is controlled by the

PMON

OUT Enable

and Interrupt Enable respectively. Interrupts are driven directly off of the status bits, whereas the

PMON

OUT pin is driven directly from the condition.

Note:

The null event does not set the Command Trigger Indicator in the

PMON

_STS register, nor

does it cause a Command Trigger that is reflected by the

PMON

OUT signal.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

PMON

_CMD0

PMON

_CMD1

PMON

_CMD2

PMON

_CMD3

PMON

_CMD4

PMON

_CMD5

PMON

_CMD6

PMON

_CMD7

+000h

+010h

+020h

+030h

+040h

+050h

+060h

+070h