41 pci configuration and status register - pcsr, 41pci configuration and status register - pcsr, 181 pci configuration and status register - pcsr – Intel CONTROLLERS 413808 User Manual

Page 327: Pci configuration and status register, Address translation unit (pci express)—intel, Bit default description, Pcie_rc

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

327

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.41 PCI Configuration and Status Register - PCSR

The PCI Configuration and Status Register has additional bits for controlling and

monitoring various features of the PCI Express interface.

Warning:

The PCI Express Bus Number and Device Number are used to form the

Requestor/Completer ID and should only be changed when operating as a Root

Complex. These fields are updated whenever a type 0 configuration write targets the

IOP. System instability may result when the Bus/Device numbers are modified while

operating as an endpoint.

Table 181. PCI Configuration and Status Register - PCSR (Sheet 1 of 2)

Bit

Default

Description

31:24

00H

PCI Express Bus Number

23:19

0_0000

2

PCI Express Device Number

18:16

000

2

PCI Express Function Number

15

0

2

Outbound Transaction Queue Busy:

0 = Outbound Transaction Queue Empty

1 = Outbound Transaction Queue Busy

Note:

This tracks outbound transactions and includes the Outbound Non-Posted, Outbound Posted,

and Inbound Completion queues.

14

0

2

Inbound Transaction Queue Busy:

0 = Inbound Transaction Queue Empty

1 = Inbound Transaction Queue Busy

Note:

This tracks inbound transactions and includes the Inbound Non-Posted, Inbound Posted, and

Outbound Completions queues.

13

Varies with

external state

of the

PCIE_RC#

strap.

PCI Express Root Complex mode

0 = PCI Express Root Complex enabled

1 = PCI Express Root Complex disabled (end point mode).

12

0

Link Layer Retry Buffer (LLRB) Busy.

0 = LLRB Empty

1 = LLRB Busy

11:10

00

2

Reserved

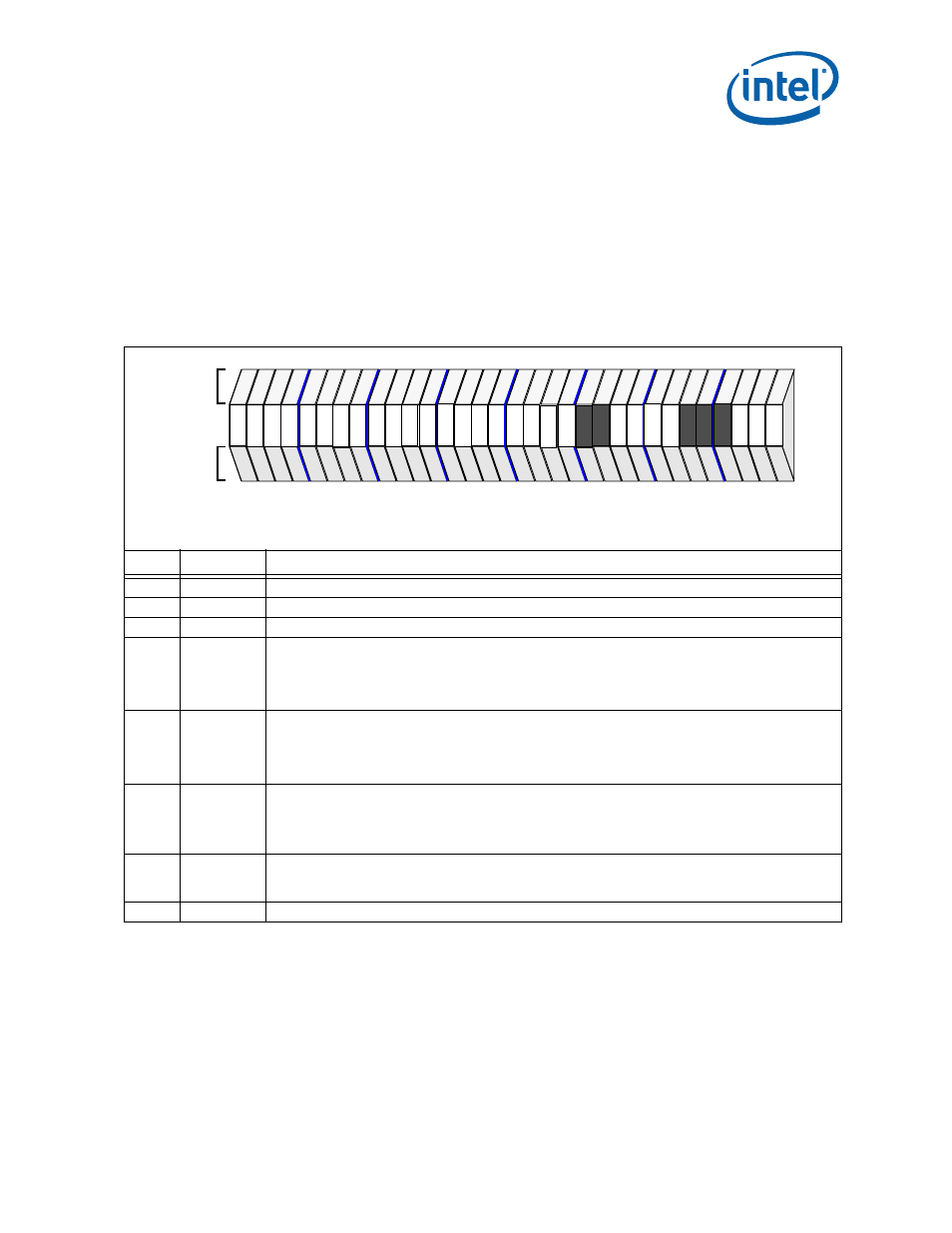

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rv

rv

rv

rv

rw

rw

rw

rw

rc

rc

rw

rw

rv

rv

rv

rv

rv

rv

rw

ro

co

co

co

co

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

CO = Clear Only

Internal Bus Address Offset

+074H