122 pci interface error descriptor log, 123 atu reset control register - aturcr, Table 263. atu reset control register - aturcr – Intel CONTROLLERS 413808 User Manual

Page 397: 122pci interface error descriptor log, 123atu reset control register - aturcr, 262 pci interface error descriptor log - pie_dlog, 263 atu reset control register - aturcr, Lk_dn_rst_bypass, Address translation unit (pci express)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

397

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.122 PCI Interface Error Descriptor Log

Descriptor log for transaction errors.

Note:

In 4138xx, bits[30:0] of this register is copied directly from the USER_ATTR[65:35]

sideband bus.

3.17.123 ATU Reset Control Register - ATURCR

This register controls the link down reset bypass strap (

LK_DN_RST_BYPASS#

)

.

Note:

Some bits in this register are sticky through reset.

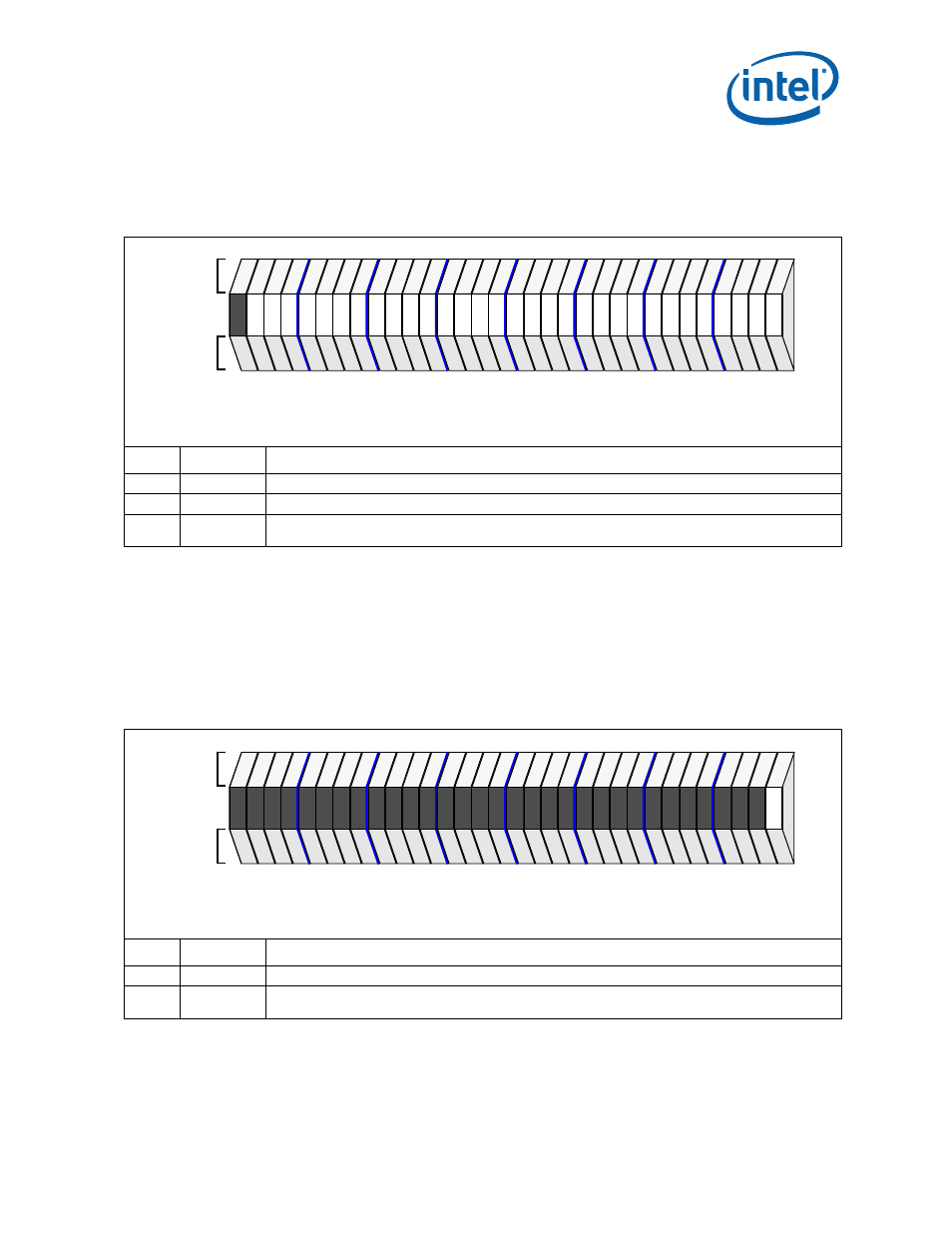

Table 262. PCI Interface Error Descriptor Log - PIE_DLOG

Bit

Default

Description

31

0

Reserved

30:29

00

DMA Channel Number

28:0

0H

ADMA Descriptor Address The DMA type can be determined by the Initiator ID in the

Error Control and Status Register - PIE_CSR”

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+39CH

Table 263. ATU Reset Control Register - ATURCR

Bit

Default

Description

31:01

0H

Reserved

00

0H

Link Down Reset Bypass override - When this bit is set, the Link Down Reset Bypass strap is ignored and

treated as when it is deasserted.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

v

rv

rv

rv

rv

rv

rv

rw

rw

S

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+3B0H