1 internal units, 1 peripheral bus interface unit, Table 524. pbi base address offset – Intel CONTROLLERS 413808 User Manual

Page 801: Table 525. peripheral bus interface unit, 524 pbi base address offset, 525 peripheral bus interface unit, Peripheral bus interface unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

801

Peripheral Registers—Intel

®

413808 and 413812

19.6.1

Internal Units

19.6.1.1 Peripheral Bus Interface Unit

The Peripheral Bus Interface Unit (PBI) is allocated 128 Bytes of PMMR registers space

and is always located at offset +1580H relative to the PMMRBAR.

Use the following equation to calculate the actual register address:

Internal Bus Address = PMMRBAR + PBI Base Address Offset + Register Offset.

Note:

Additionally, GPIO[8:0] I/O pad control registers are located in the

registers block.

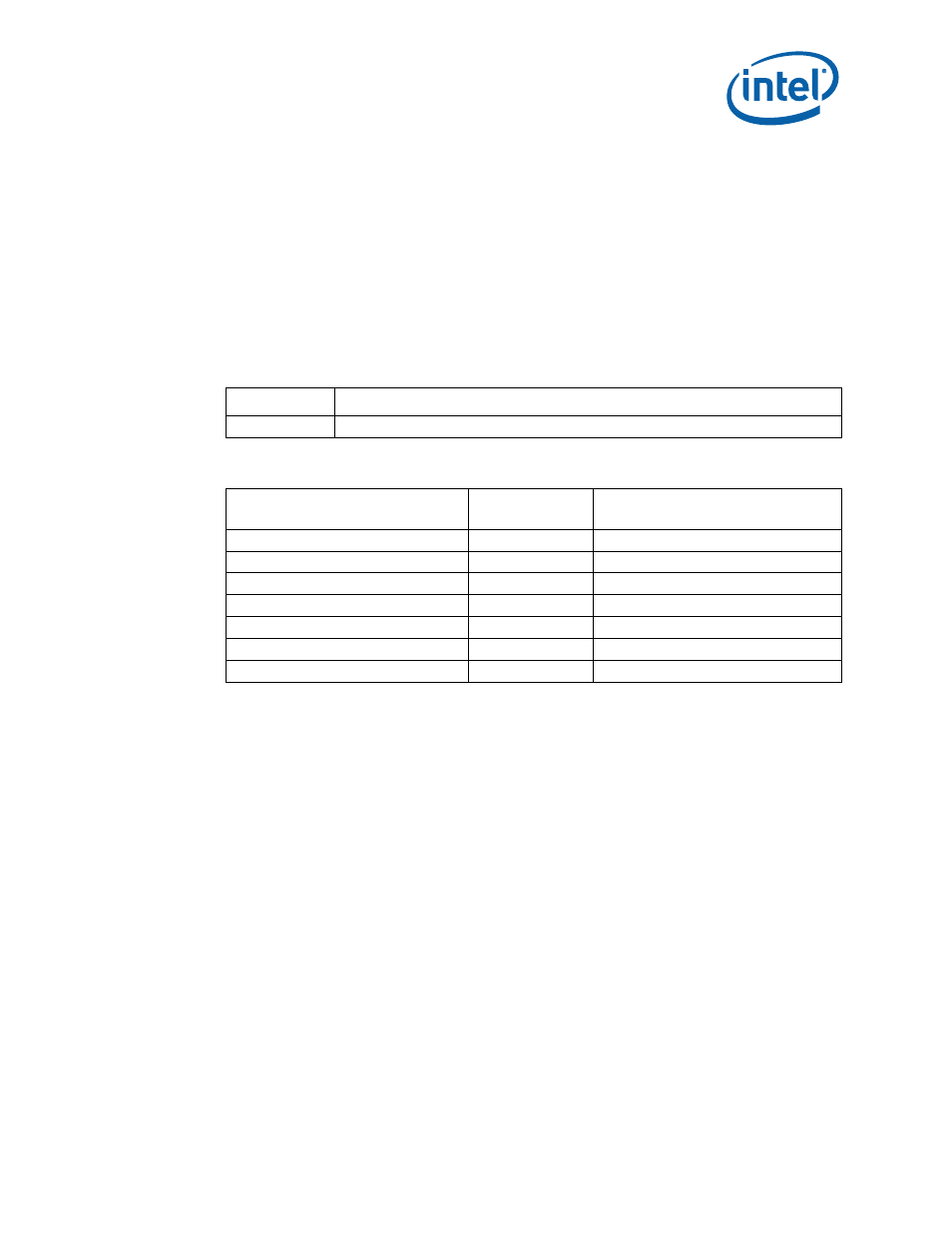

Table 524. PBI Base Address Offset.

Unit

PBI Base Address Offset (Relative to PMMRBAR)

PBI

+1580H

Table 525. Peripheral Bus Interface Unit

Register Description (Name)

Register Size in

Bits

Internal Bus Address Offset (Relative

to PBI Base Address Offset)

PBI Control Register — PBCR

32

+00H

PBI Status Register — PBISR

32

+04H

PBI Base Address Register 0 — PBBAR0

32

+08H

PBI Limit Register 0 — PBLR0

32

+0CH

PBI Base Address Register 1 — PBBAR1

32

+10H

PBI Limit Register 1 — PBLR1

32

+14H

Reserved

x

+18H through +7FH