Table 331. data parity testing completer ids, 330 address and data parity testing initiator ids, 331 data parity testing completer ids – Intel CONTROLLERS 413808 User Manual

Page 489: Table 331

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

489

System Controller (SC) and Internal Bus Bridge—Intel

®

413808 and 413812

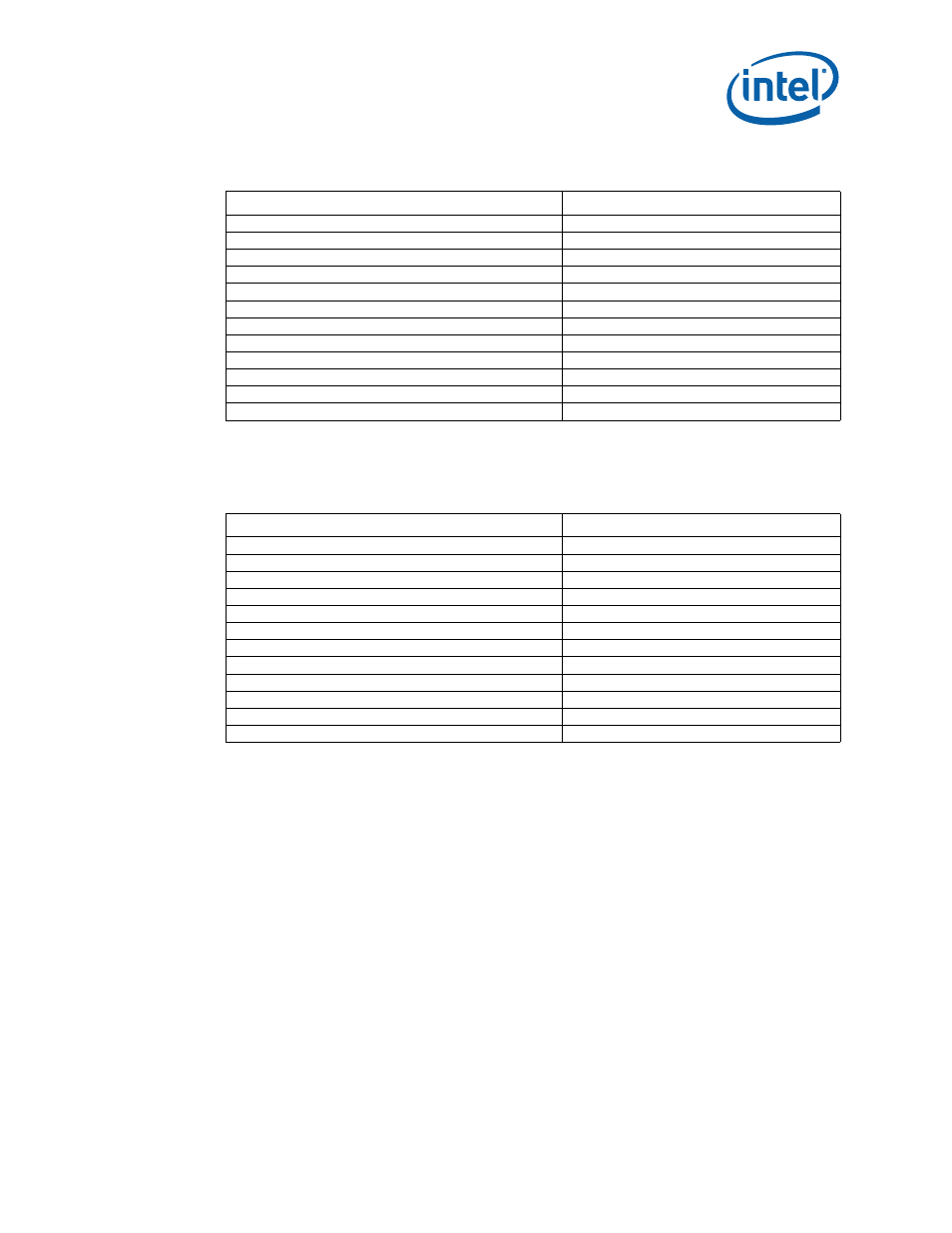

Table 330. Address and Data Parity Testing Initiator IDs

Internal Bus Initiator

Initiator ID

Reserved

0000

2

Intel XScale

®

processor 0 (coreID = 0)

0001

2

Intel XScale

®

processor 1 (coreID = 1)

0010

2

ATU-X

0011

2

ATU-E

0100

2

Reserved

0101

2

Reserved

0110

2

Messaging Unit

0111

2

Reserved

1000

2

SMBus and

PMON

1001

2

Reserved

1010

2

Reserved

1011

2

through 1111

2

Note:

This table contains the Initiator IDs for injecting address parity error when these initiators are making

address requests. In addition these same Initiator IDs can be used when injecting data parity error

when these initiators are pushing data during writes.

Table 331. Data Parity Testing Completer IDs

Internal Bus Initiator

Initiator ID

Reserved

0000

2

Not Applicable

a

a. Not applicable implies that the ID associated with that initiator does not return completion data.

0001

2

Not Applicable

0010

2

ATU-X

0011

2

ATU-E

0100

2

Reserved

0101

2

Reserved

0110

2

Messaging Unit

0111

2

Reserved

1000

2

UART, I2C, GPIO, PBI, and

PMON

1001

2

Not Applicable

1010

2

Reserved

1011

2

through 1111

2

Note:

This table contains the Initiator IDs for injecting data parity error when these Initiators are returning

data during read completions. Note that in this scenario the initiator of the data transaction is the

actual completer.