2 stop phase, Figure 75. stop (p) signaling, 3 ack/nack – Intel CONTROLLERS 413808 User Manual

Page 646: Figure 76. ack (a) signaling, Figure 77. nack (n) signaling, 4 wait states, 75 stop (p) signaling, 76 ack (a) signaling, 77 nack (n) signaling, Smbdat

Intel

®

413808 and 413812—SMBus Interface Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

646

Order Number: 317805-001US

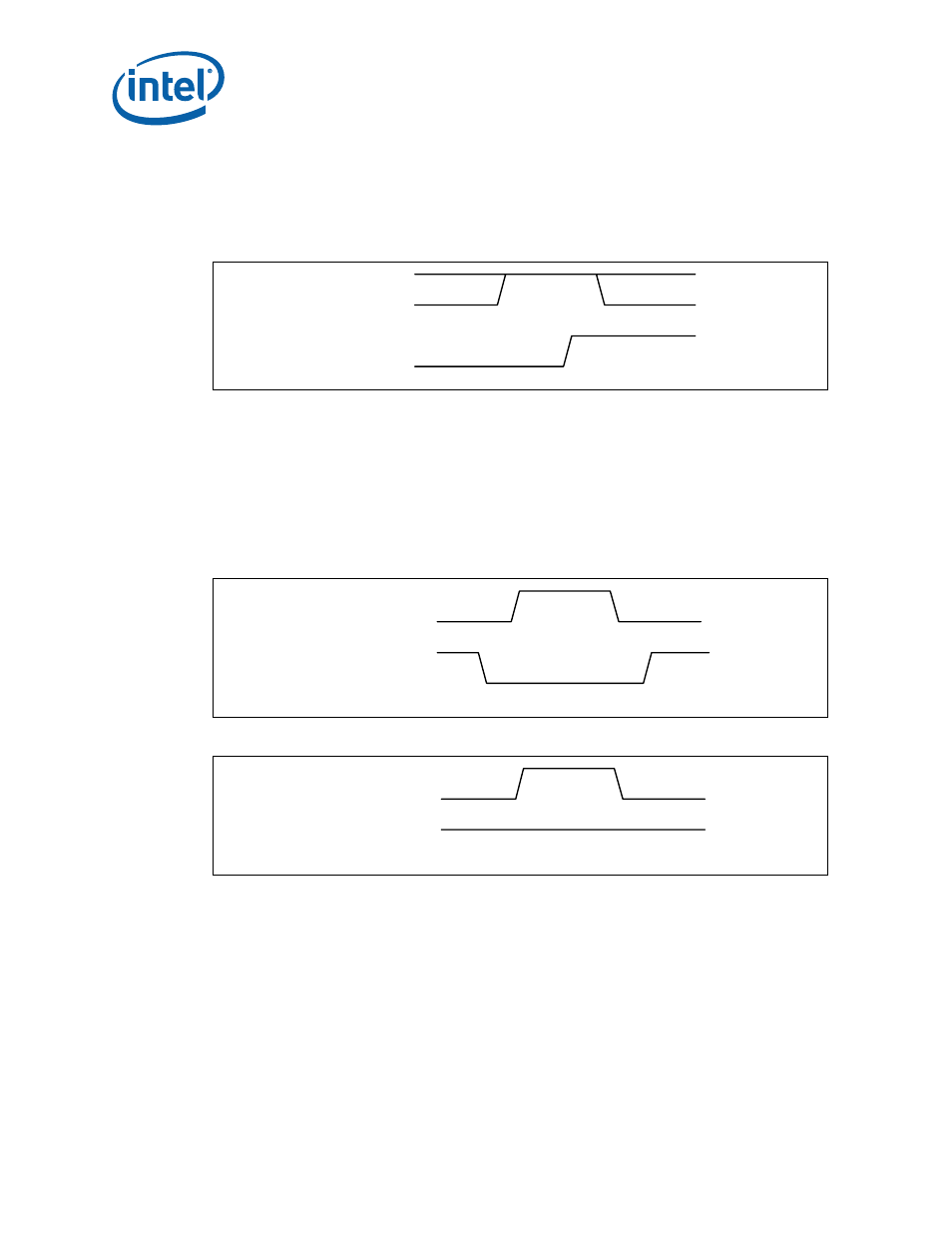

12.3.2.2.2 Stop Phase

A stop condition is generated when SMBus is busy to indicate that its state is changing

to idle. The Stop condition occurs when

SMBDAT

transitions from Low to High while

SMBCLK

remains High.

A stop bit can occur at any point in a data stream. It is not insured to occur after an

ACK from a target (as later waveforms show). The 4138xx must be able to accept a

stop condition at any time and clean up.

12.3.2.2.3 ACK/NACK

For every 8 bits of data transfer (including address and direction), the receiving agent

must respond with ACK or NACK. An ACK is requires

SMBDAT

= 0 during

SMBCLK

=

1. A NACK requires

SMBDAT

= 1 during

SMBCLK

= 1 as shown below.

During a write cycle, the 4138xx must drive an ACK after the address/direction phase,

and after the data phase. During a read cycle, the 4138xx must drive an ACK/NACK

after the address/direction phase, and (when ACKed) the initiator must drive an

ACK/NACK after the 4138xx returns its 8 bits of data.

12.3.2.2.4 Wait States

The receiver (initiator or target) can add wait states, after driving ACK for receiving the

last byte, by driving the

SMBCLK

line low. Further data transfers are delayed until the

receiver stops driving

SMBCLK

low. It is expected the 4138xx drives the

SMBCLK

line

low after receiving data on writes until the write is complete, and after receiving the

direction bit on reads until the read data is ready.

Figure 75. Stop (P) Signaling

SMBCLK

SMBDAT

B6278-01

Figure 76. ACK (A) Signaling

Figure 77. NACK (N) Signaling

SMBCLK

SMBDAT

B6279-01

SMBCLK

SMBDAT

B6280-01