Table 4. outbound address translation control, 7 4 gbyte section 0 of the internal bus memory map, 4 outbound address translation control – Intel CONTROLLERS 413808 User Manual

Page 68

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

68

Order Number: 317805-001US

2.2.2.1

Outbound Address Translation - Internal Bus Transactions

In addition to providing the mechanism for inbound translation, the ATU translates Intel

XScale

®

processor-initiated cycles to the PCI bus. This is known as outbound address

translation. Outbound transactions are processor or ADMA transactions targeted at the

PCI bus. The ATU internal bus target interface claims internal bus cycles and completes

the cycle on the PCI bus on behalf of the Intel XScale

®

processor or ADMA.

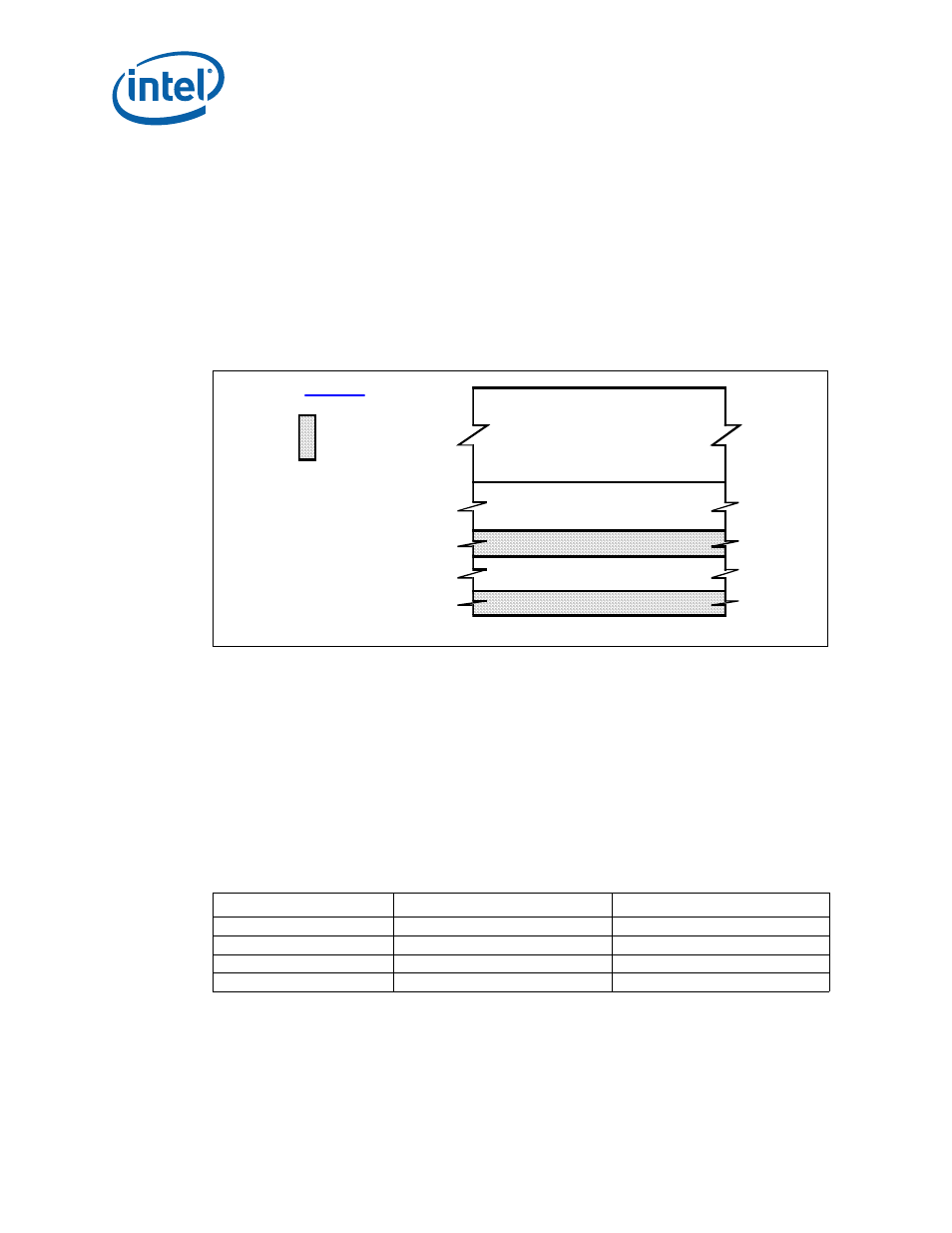

shows 4 Gbyte memory section 0 (Internal Bus Address [35:32] = 0000

2

) of

the 4138xx memory map with all reserved address locations highlighted. By default,

the 64KByte outbound I/O window is from 0.FFFB.0000H to 0.FFFB.FFFFH while the

PMMR registers, by default, reside from 0 FFD8.0000H to 0 FFDF.FFFFH.

By default, Outbound Memory Window 0, Outbound Memory Window 1, Outbound

Memory Window 2, and Outbound Memory Window 3 reside in 4 Gbyte memory

sections 1, 2, 3 and 4 respectively, of the 64 Gbyte Internal Bus address space.

The ATU response to Outbound Transactions is globally controlled by the ATU

Configuration Register Outbound Enable bit, as well as the Bus Master Enable bit in

each function. When the Outbound Enable bit is deasserted, the internal bus outbound

transaction master-abort are not forwarded to the PCI Express Domain. When the

Outbound Enable bit is asserted, the relevant Bus Master Enable bit for each function

determines appropriate response to an outbound transaction.

describes the Outbound ATUs behavior for the different combinations of these

control bits.

Figure 7.

4 Gbyte Section 0 of the Internal Bus Memory Map

0 0000 0000H

AD DRES S

0 FFDF FFFFH

Address Space

Used

0 FFD8 0000H

0 FFFB 0000H

0 FFFB FFFFH

0 FFFC FFFFH

0 FFFF FFFFH

for other Resources

External Memory

Outbound I/O Window

(Default)

Code/Data

Peripheral Memory-Mapped Registers

(Default)

B6324-01

Table 4.

Outbound Address Translation Control

Outbound Response

Outbound Enable

a

(ATUCR[1])

a. In addition, the outbound memory windows need to be individually enabled in order to claim. When, disabled,

the outbound memory windows does not claim. By default, Outbound Memory Window 0, and Outbound

Memory Window 1 are enabled. Outbound Memory Windows 2 and 3 are disabled by default.

Bus Master Enable

b

b. In a multi-function configuration, each function independently controls its own Bus Master Enable bit.

Master-Abort

0

0

Master-Abort

0

1

Retry

1

0

Claim

c

c. The ATU may respond with a Retry in this case when the Outbound Transaction Queues are full.

1

1