5 atu command register - atucmd, Table 144. atu command register - atucmd, 144 atu command register - atucmd – Intel CONTROLLERS 413808 User Manual

Page 298: Section 3.17.5, “atu command register - atucmd” on, Atu command register - atucmd, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

298

Order Number: 317805-001US

3.17.5

ATU Command Register - ATUCMD

ATU Command Register bits adhere to the definitions in the PCI Local Bus Specification,

Revision 2.3 and in most cases, affect the behavior of the PCI ATU and devices on the

PCI Express Link.

Table 144. ATU Command Register - ATUCMD

Bit

Default

Description

15:11

00000

2

Reserved

10

0

2

Interrupt Disable - Controls the ability of the ATU to generate INTx interrupt messages.

When set, the ATU is prevented from generating INTx interrupt messages and generates a

Deassert_INTx message for any emulation interrupts already asserted.

09

0

2

Fast Back to Back Enable - Does not apply to PCI Express. Hard-wired to 0.

08

0

2

SERR#

Enable - When set, the ATU is allowed to report non-fatal and fatal error detected by 4138xx to

the Root Complex.

Note:

Errors are reported either through this bit or through the PCI-Express specific bits in the

Express Device Control Register - PE_DCTL

07

0

2

Address/Data Stepping Control - Does not apply to PCI Express. Hard-wired to 0.

06

0

2

Parity Error Response - When set, the ATU takes normal action in response to a poisoned TLP received

from PCI Express. When cleared, parity checking is disabled.

Note:

When the bit is cleared but the Poisoned TLP Mask is cleared in the

register, the ATU still logs the error in the Advanced Error Reporting

registers and generate an Uncorrectable Error message.

05

0

2

VGA Palette Snoop Enable - Does not apply to PCI Express. Hard-wired to 0.

04

0

2

Memory Write and Invalidate Enable - Does not apply to PCI Express. Hard-wired to 0.

03

0

2

Special Cycle Enable - Does not apply to PCI Express. Hard-wired to 0.

02

0

2

Bus Master Enable - When cleared, the ATU is prevented from issuing any memory or I/O read/write

requests. Requests other than memory or I/O requests are not controlled by this bit.

The ATU initiates a completion transaction regardless of the setting.

01

0

2

Memory Enable - Controls the ATU interface’s response to memory transactions. When cleared, the ATU

drops the transaction and returns an unsupported request

00

0

2

I/O Space Enable - Controls the ATU interface response to I/O transactions. When cleared, the ATU

drops the transaction and returns an unsupported request.

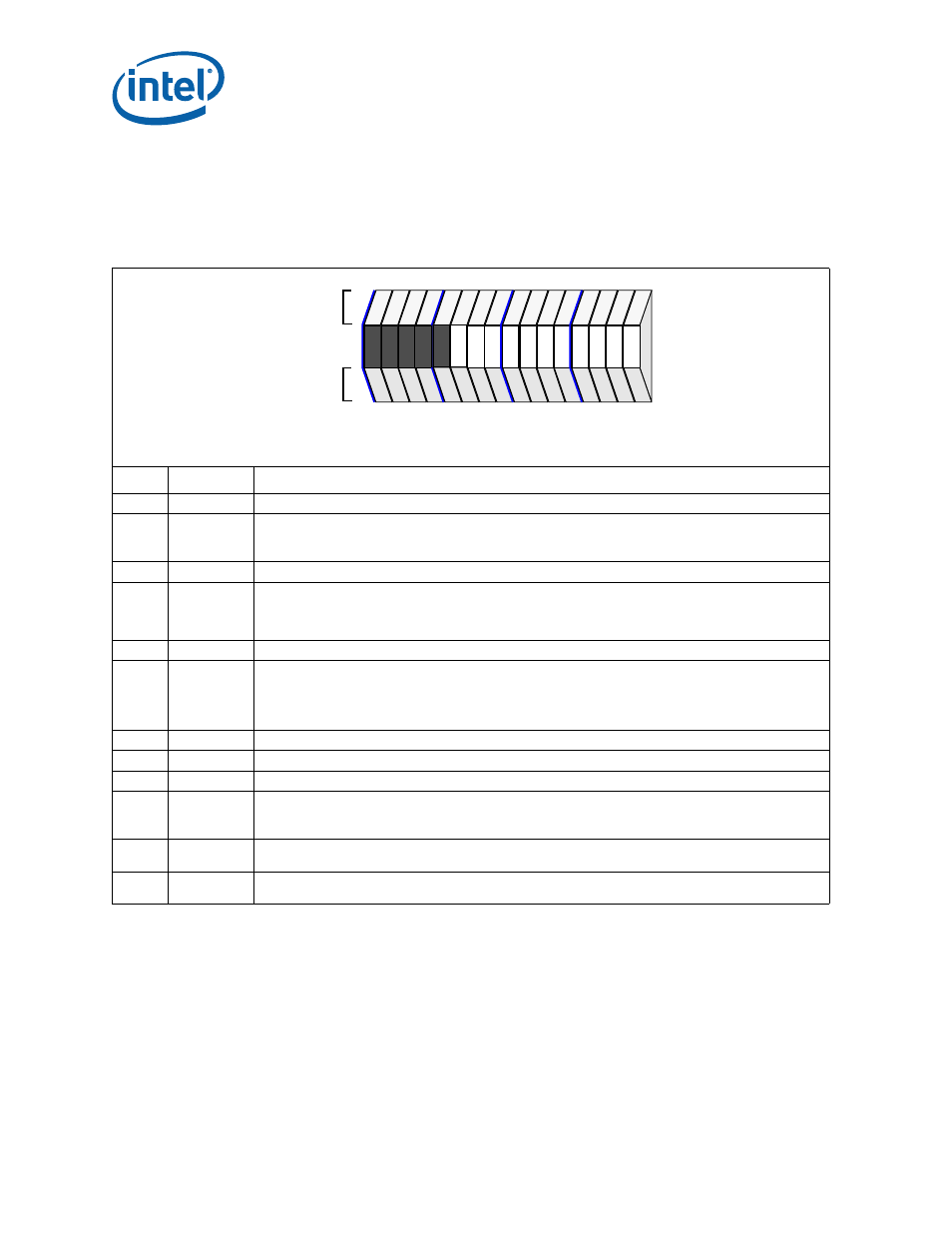

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

ro

ro

rw

rw

ro

ro

rw

rw

ro

ro

ro

ro

ro

ro

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+004H