Table 472. i, C status register x — isrx (sheet 2 of 2), Intel – Intel CONTROLLERS 413808 User Manual

Page 718: C bus interface units, Arbitration loss detected, Slave stop detected, Bus busy, Unit busy, Ack/nack status, Read/write mode

Intel

®

413808 and 413812—I

2

C Bus Interface Units

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

718

Order Number: 317805-001US

05

0

2

Arbitration Loss Detected

: used during multi-master operation.

0 = Cleared when arbitration is won or never took place.

1 = Set when the I

2

C unit loses arbitration.

04

0

2

Slave STOP Detected

:

0 = No STOP detected.

1 = Set when the I

2

C unit detects a STOP while in slave-receive or slave-transmit mode.

03

0

2

I

2

C

Bus Busy

:

0 = I

2

C bus is idle or the I

2

C unit is using the bus (i.e., unit busy).

1 = Set when the I

2

C bus is busy but the 4138xx

I

2

C unit is not involved in the transaction.

02

0

2

Unit Busy

:

0 = I

2

C unit not busy.

1 = Set when the 4138xx

I

2

C unit is busy. This is defined as the time between the first START and

STOP.

01

0

2

Ack/Nack Status

:

0 = The I

2

C unit received or sent an Ack on the bus.

1 = The I

2

C unit received or sent a Nack.

This bit is used in slave transmit mode to determine when the byte transferred is the last one. This bit is

updated after each byte and Ack/Nack information is received.

00

0

2

Read/Write Mode

:

0 = The I

2

C unit is in master-transmit or slave-receive mode.

1 = The I

2

C unit is in master-receive or slave-transmit mode.

This is the R/W# bit of the slave address. It is automatically cleared by hardware after a stop state.

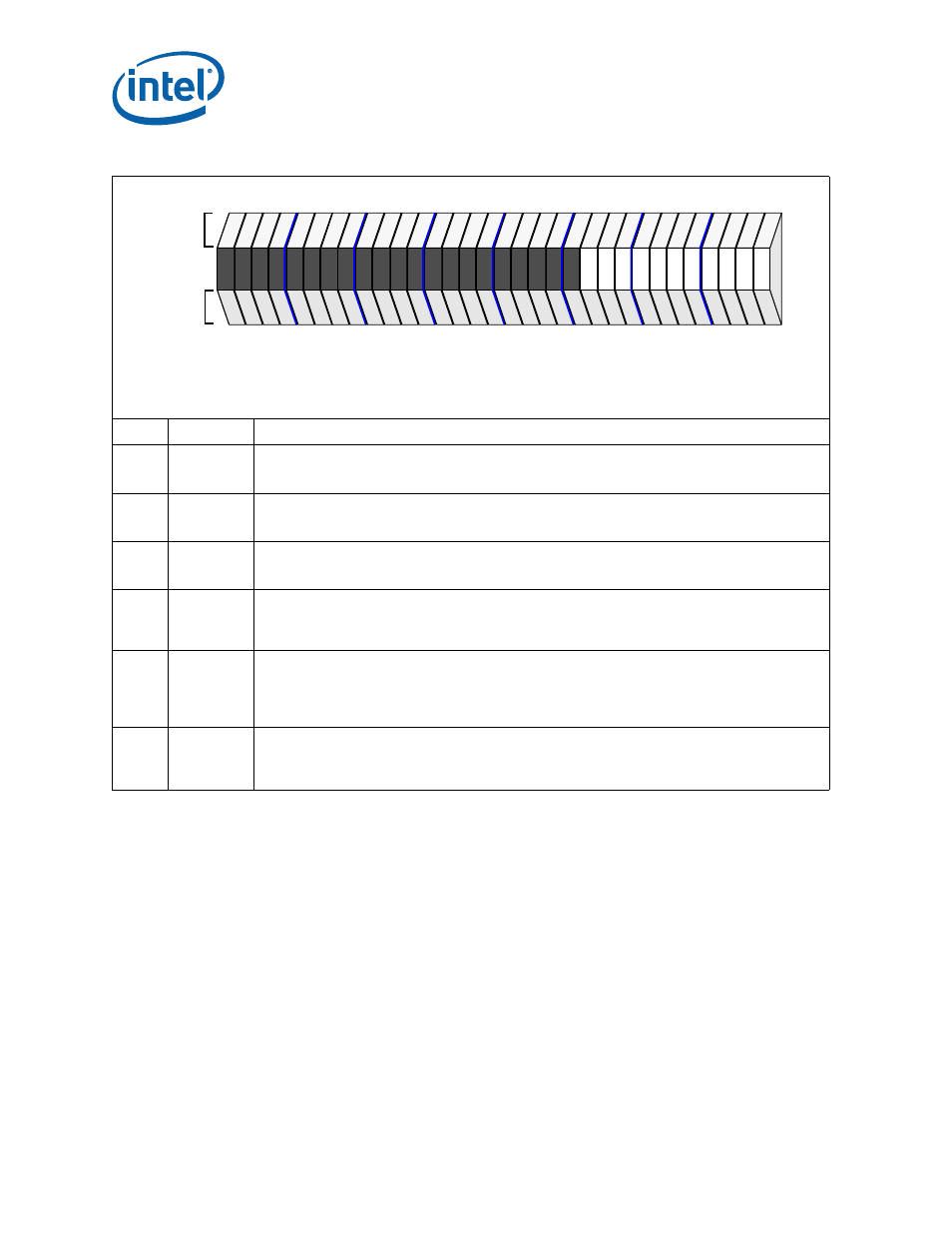

Table 472. I

2

C Status Register x — ISRx (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rc

na

rc

na

rc

na

rc

na

rc

na

rc

na

rc

na

ro

na

ro

na

ro

na

ro

na

Unit #

0

1

2

Intel XScale

®

processor internal bus address

offset

+2504H

+2524H

+2544H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible