Intel, Fw_timer_ off, Retry – Intel CONTROLLERS 413808 User Manual

Page 328: P_rst, Rst_mode[ 1:0, Rst_mode[1:0, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

328

Order Number: 317805-001US

9:8

00

Core reset. These bits are used to place the Intel XScale

®

microarchitecture processors into reset.

When a ‘1’ is written to these bits the corresponding Core Processor Reset bit (Bits1:0) is set.

These bits are self clearing and always reads ‘0’.

07

Varies with

external state

of the

FW_TIMER_

OFF#

strap

Firmware Timer Disable

0 = Firmware Timeout is disabled.

1 = Firmware Timeout is enabled

When enabled, a 400mS timer is started at the trailing edge of reset. The Configuration Request Retry

(bit 2 of this register) is cleared when it is not cleared before the expiration of the timer. For example,

when firmware does not clear the Configuration Request Retry bit before the timer expires. The

firmware timer bit is also automatically cleared by the firmware timer when the Configuration Request

Retry bit is still set when the timer expires. After the host is allowed access, the firmware timer bit can

be used to indicate how the Configuration Request Retry bit was cleared:

0 = The firmware timer expired and cleared both the Configuration Request Retry and the firmware

timer bits.

1 = Firmware cleared the Configuration Request Retry bit before the timer expired.

Note:

When the firmware timer is disabled, firmware is responsible to clear the Configuration Request

Retry bit. Otherwise, the ATU indefinitely retries all host configuration cycles.

05:03

00

2

Reserved

02

Varies with

external state

of

RETRY

pin

at PCI

Express Link

reset

Configuration Request Retry - When this bit is set, the PCI Express interface of the 4138xx

responds to

all configuration cycles with a Completion Retry Status (CRS) condition. When clear, the 4138xx

responds to the appropriate configuration cycles.

The default condition for this bit is based on the external state of the

RETRY

pin at the rising edge of

P_RST#

. When the external state of the pin is high, the bit is set. When the external state of the pin is

low, the bit is cleared.

Note:

This bit self-clears when the Firmware Timer expires. Bit 7 of this register is used to stop the

firmware timer.

01:00

Varies with

external state

of

RST_MODE[

1:0]#

pin at

PCI Express

Link reset

Core Processor Reset - This bit is set to its default value by the hardware when either

P_RST#

is

asserted or the Reset Internal Bus bit in PCSR is set. When this bit is set, the Intel XScale

®

processor is

being held in reset. Software cannot set this bit. Software is required to clear this bit to deassert Intel

XScale

®

processor reset.

The default condition for this bit is based on the external state of the

RST_MODE[1:0]#

pin at the

rising edge of

P_RST#

. When the external state of the pin is low, the default value of this bit is set.

When the external state of the pin is high, the default value of this bit is clear.

Note:

This bits are “Clear Only”. A write of ‘0’ clears the bit, a write of ‘1’ has no affect.

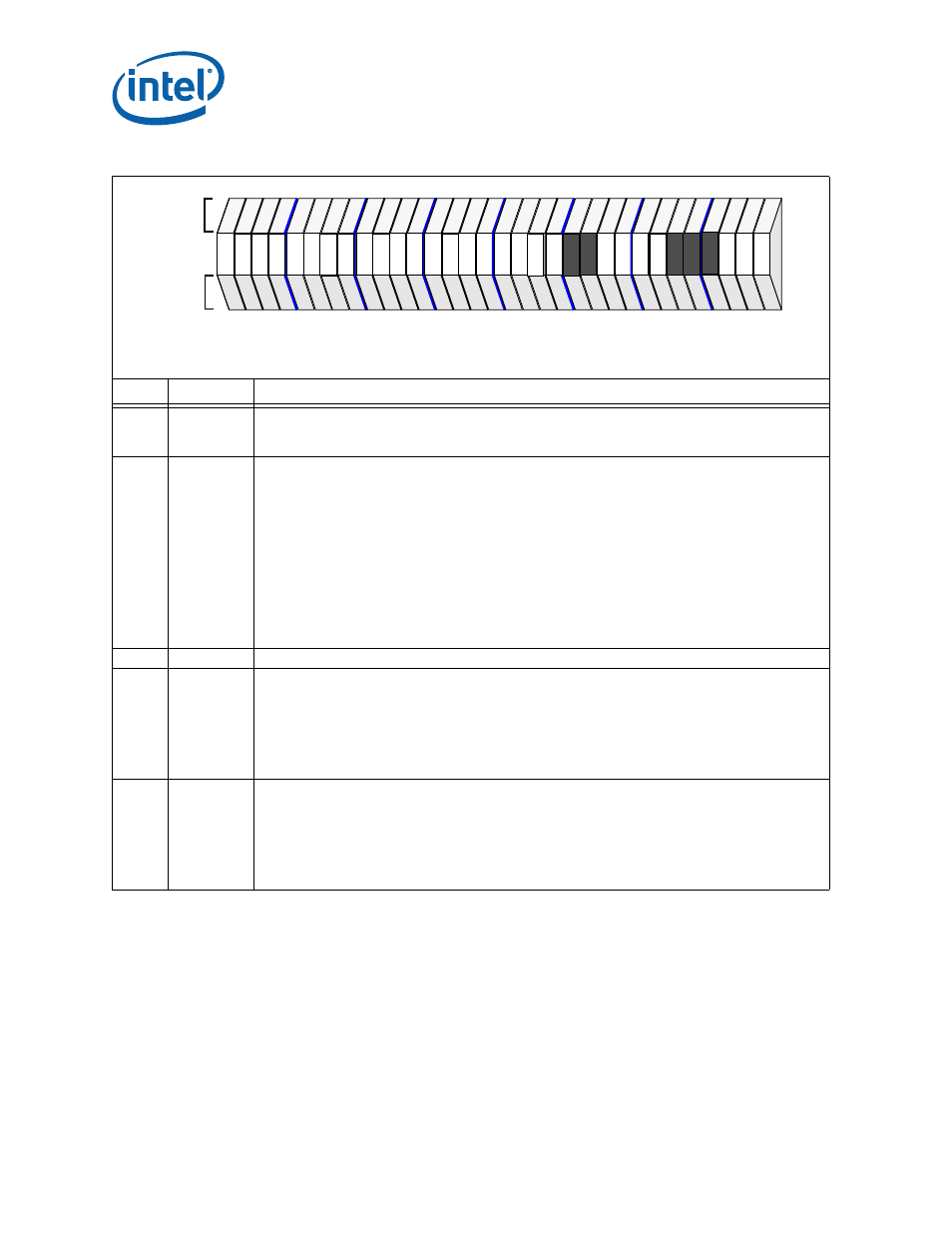

Table 181. PCI Configuration and Status Register - PCSR (Sheet 2 of 2)

Bit

Default

Description

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

rw

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

rv

rv

rv

rv

rw

rw

rw

rw

rc

rc

rw

rw

rv

rv

rv

rv

rv

rv

rw

ro

co

co

co

co

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

CO = Clear Only

Internal Bus Address Offset

+074H