Equation 8. inbound address detection, Figure 24. inbound address detection, 24 inbound address detection – Intel CONTROLLERS 413808 User Manual

Page 238

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

238

Order Number: 317805-001US

•

Section 3.17.16, “Inbound ATU Base Address Register 1 - IABAR1” on page 308

• Section 3.17.31, “Inbound ATU Limit Register 1 - IALR1” on page 320

•

Section 3.17.32, “Inbound ATU Translate Value Register 1 - IATVR1” on page 321

•

Section 3.17.33, “Inbound ATU Upper Translate Value Register 1 - IAUTVR1” on

The ATU uses the following registers in inbound address window 2 translation:

•

Section 3.17.18, “Inbound ATU Base Address Register 2 - IABAR2” on page 310

• Section 3.17.34, “Inbound ATU Limit Register 2 - IALR2” on page 322

•

Section 3.17.35, “Inbound ATU Translate Value Register 2 - IATVR2” on page 323

•

Section 3.17.36, “Inbound ATU Upper Translate Value Register 2 - IAUTVR2” on

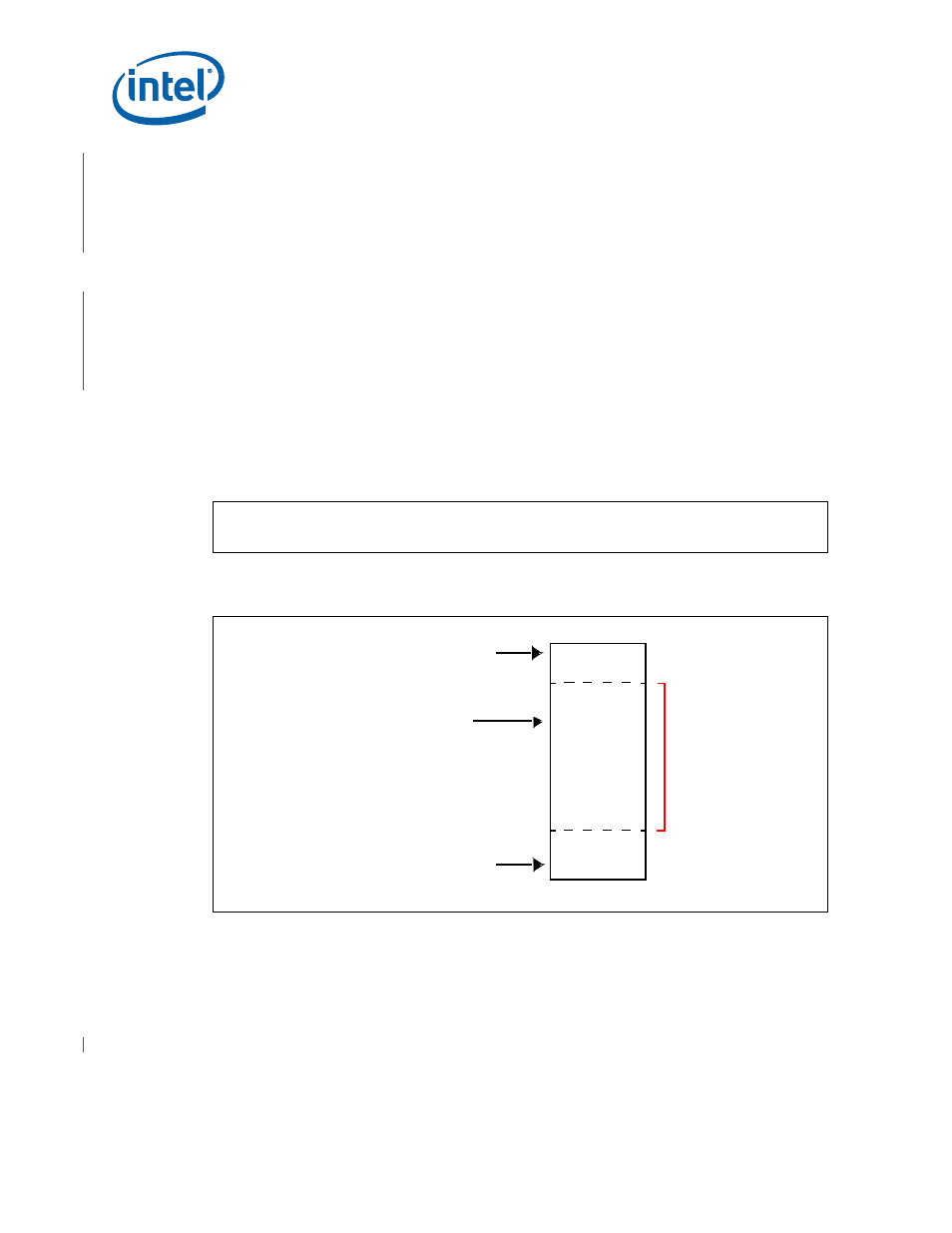

Inbound address detection is determined by comparing the 64-bit PCI address with the

base address register and the limit register. In the case of 3DW headers, the upper

32-bits of the address is assumed to be 0000_0000h during address comparison. The

algorithm for detection is:

shows an example of inbound address detection.

The lower 32-bits of the incoming address is bitwise ANDed with the associated

inbound limit register. When the result matches the base register, the inbound PCI

address is detected as being within the inbound translation window and is claimed by

the ATU. When the address is outside the translation window, the ATU terminates the

transaction as an Unsupported Request (UR).

Note:

By default, the first 8Kbytes of the ATU inbound address translation window 0 are

reserved for the Messaging Unit. See

Section 3.5, “Messaging Unit” on page 257

.

Equation 8. Inbound Address Detection

When PCI_Address [31:0] & Limit_Register[31:0] == Base_Register[31:0] and

PCI_Address [63:32] == Base_Register[63:32] the PCI Address is translated by the Inbound ATU.

Otherwise treat as an Unsupported Request.

Figure 24. Inbound Address Detection

PCI Address

Space

Base_Register

Base_Register + Value of Limit_Register

Inbound

Translation

Window

Address is claimed

Address is not claimed

Unsupported Request

Address is not claimed

Unsupported Request

B6334-01