6 inbound vendor_defined message transactions, 121 inbound vendor_defined message type 0 response – Intel CONTROLLERS 413808 User Manual

Page 243

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

243

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.3.1.6

Inbound Vendor_Defined Message Transactions

Inbound messages are routed to the PCI Express message unit where they are decoded

and processed.

Inbound Vendor_Defined Messages (IVM) are logged in the Inbound Message

Header0-3 and Inbound Message Payload registers and an interrupt is conditionally

sent to the Intel XScale

®

processor.

Only one message can be pending in the Inbound Vendor Message registers at one

time. When bit 6 of the

“ATU Configuration Register - ATUCR” on page 326

is set, then

subsequent IVM are dropped. This is necessary to prevent deadlock when the Intel

XScale

®

processor has outstanding read transactions.

When bit 6 is cleared, then when a second vendor specific message transaction reaches

the head of the IPHQ it stalls until the message registers are freed by clearing the

Message Received bit in the ATUISR. Since messages are posted transactions, they stall

all other transactions until they make progress.

When the message received interrupt mask is set in the ATUMR, then the inbound

message transactions are still logged to the Inbound message register but they do not

block following vendor specific message transactions.

Note:

A Type0 vendor_defined message may be discarded without a UR response when the

interrupt mask is cleared and the ATU is configured to drop subsequent IVM messages

when the interrupt is pending.

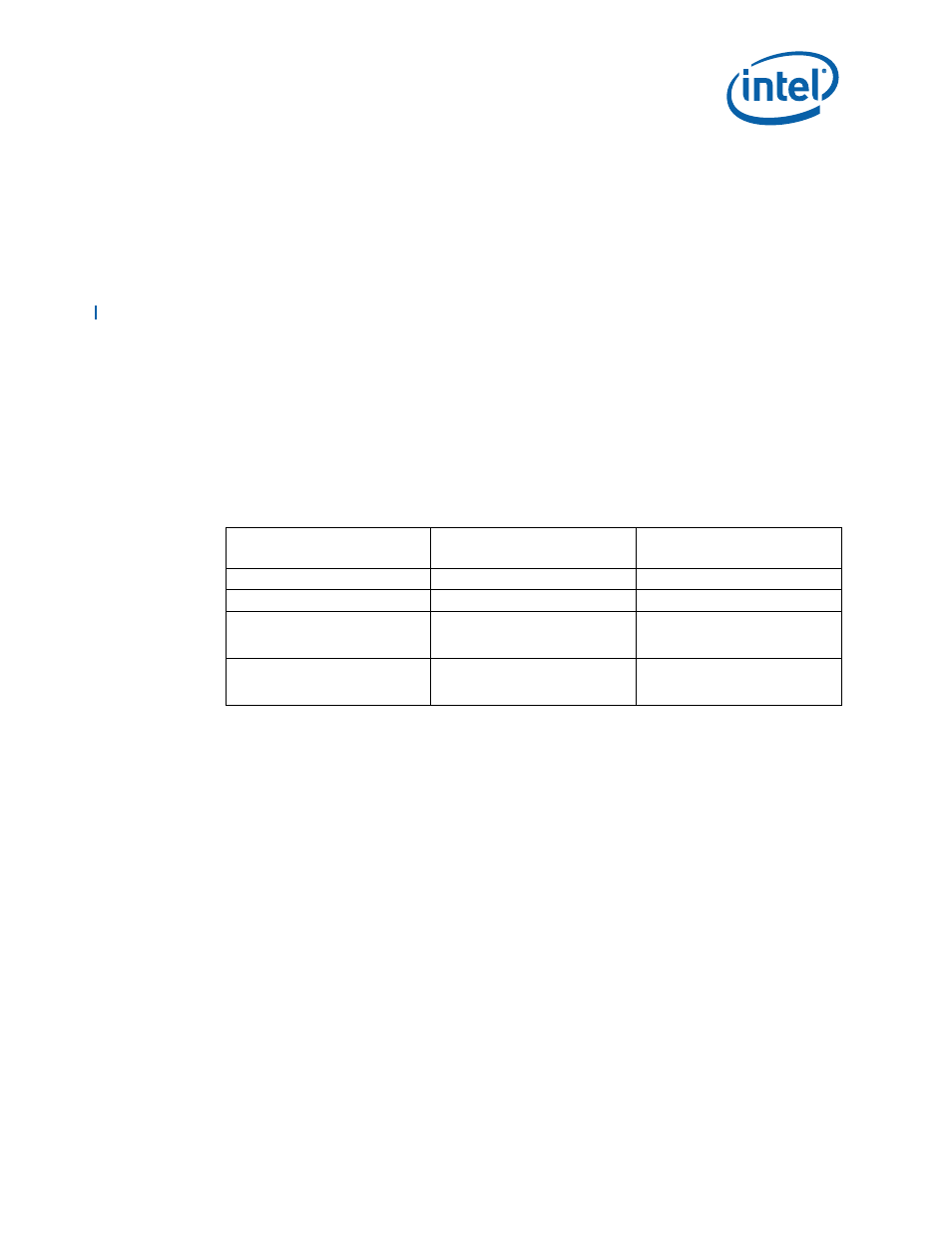

Table 121. Inbound Vendor_Defined Message Type 0 Response.

Response for Type 0 IVM

IVM Received Interrupt Mask

(ATUIMR - bit 25)

Drop subsequent IVM

(ATUCR - bit 6)

Unsupported Request (UR)

1

0

UR

1

1

Return UR when firmware requests

a UR response.

(PEMCSR -bit 14).

0

0

Dropped Silently when interrupt

pending

(ATUISR - bit 25).

0

1