Intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 334

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

334

Order Number: 317805-001US

3.17.45 PCI Express Link Control/Status Register - PELCSR

The PCI Express Link Control/Status Register controls various parameters of the Link

Layer including Training Sequence.

Note:

When operating as an endpoint, these bits operate as status bits and reflect the

settings of the most recent TS1/TS2 training sequences. When operating as a Root

Complex, these bits are control bits that are used when sending the training

sequences. Training sequences can be initiated by setting the Retrain Link bit in the

“PCI Express Link Control Register PE_LCTL” on page 348

Table 185. PCI Express Link Control and Status Register - PELCSR

Bit

Default

Description

31:6

0000H

Reserved

5

Scrambling Disabled Status

0 = Scrambling Active

1 = Scrambling Disabled

4

Loopback Status

0 = Loopback Disabled

1 = Loopback Enabled

3

0

Disable Scrambling - This controls the disable scrambling bit in the TS1 Ordered Set.

0 = Scrambling Active

1 = Scrambling Disabled

2

0

Loopback - This controls the loopback bit in the TS1 Ordered Set.

0 = Loopback Disabled

1 = Loopback Enabled

1

0

Reserved

Note:

The Disable Link control is located in the

“PCI Express Link Control Register PE_LCTL”

0

0

Hot Reset - When operating as an endpoint, this is a status bit. When operating as a Root Complex, this

is a control bit.

0 = Hot Reset Disabled

1 = Hot Reset Enabled

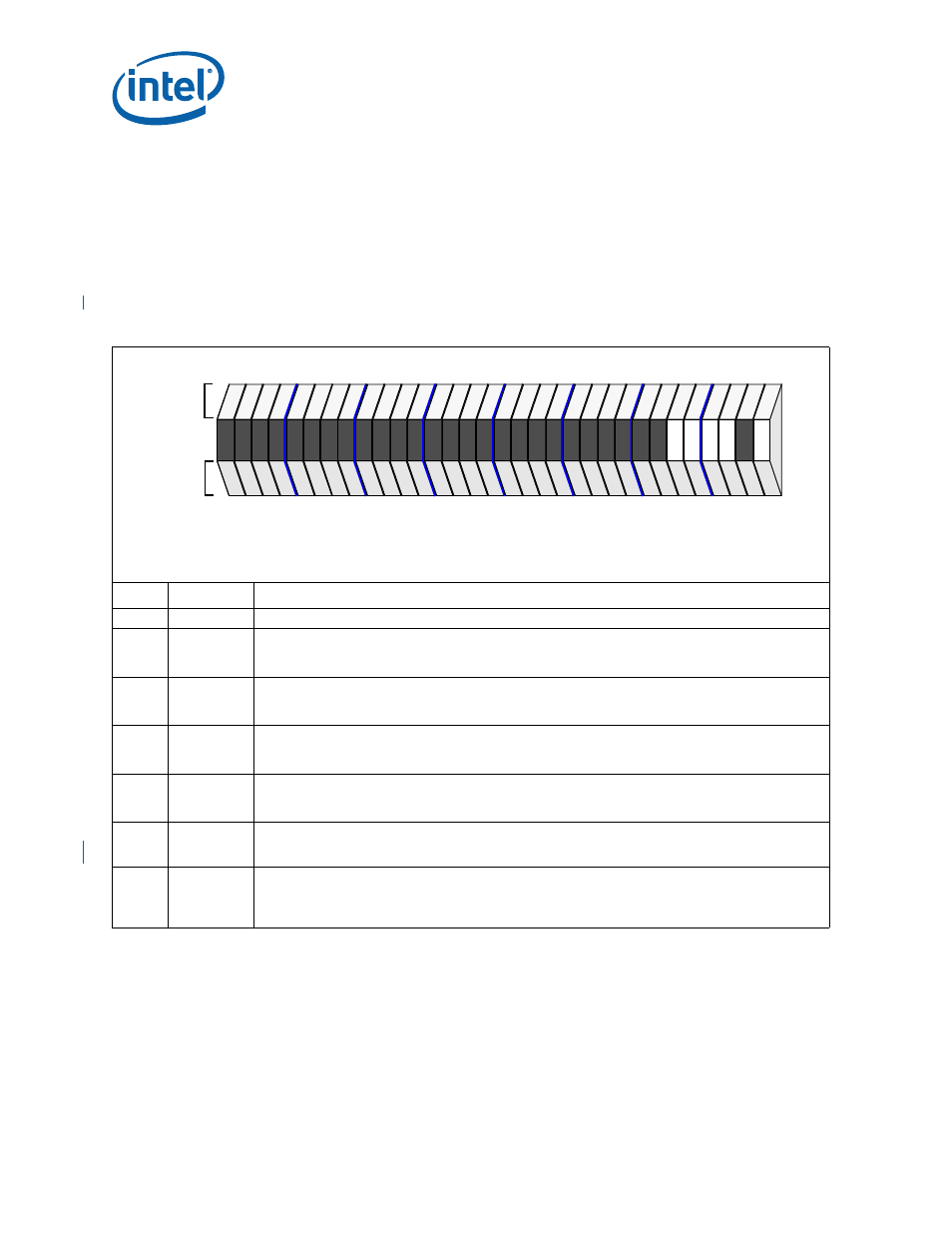

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

ro

ro

ro

ro

rw

rw

rw

rw

rv

rv

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+084H