5 atu command register - atucmd, Table 31. atu command register - atucmd, 31 atu command register - atucmd – Intel CONTROLLERS 413808 User Manual

Page 148: Atu command register - atucmd, Section, Intel, Bit default description, Int[a:d, Serr

Intel

®

413808 and 413812—Address Translation Unit (PCI-X)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

148

Order Number: 317805-001US

2.14.5

ATU Command Register - ATUCMD

ATU Command Register bits adhere to the definitions in the PCI Local Bus Specification,

Revision 2.3 and in most cases, affect the behavior of the PCI ATU and devices on the

PCI bus.

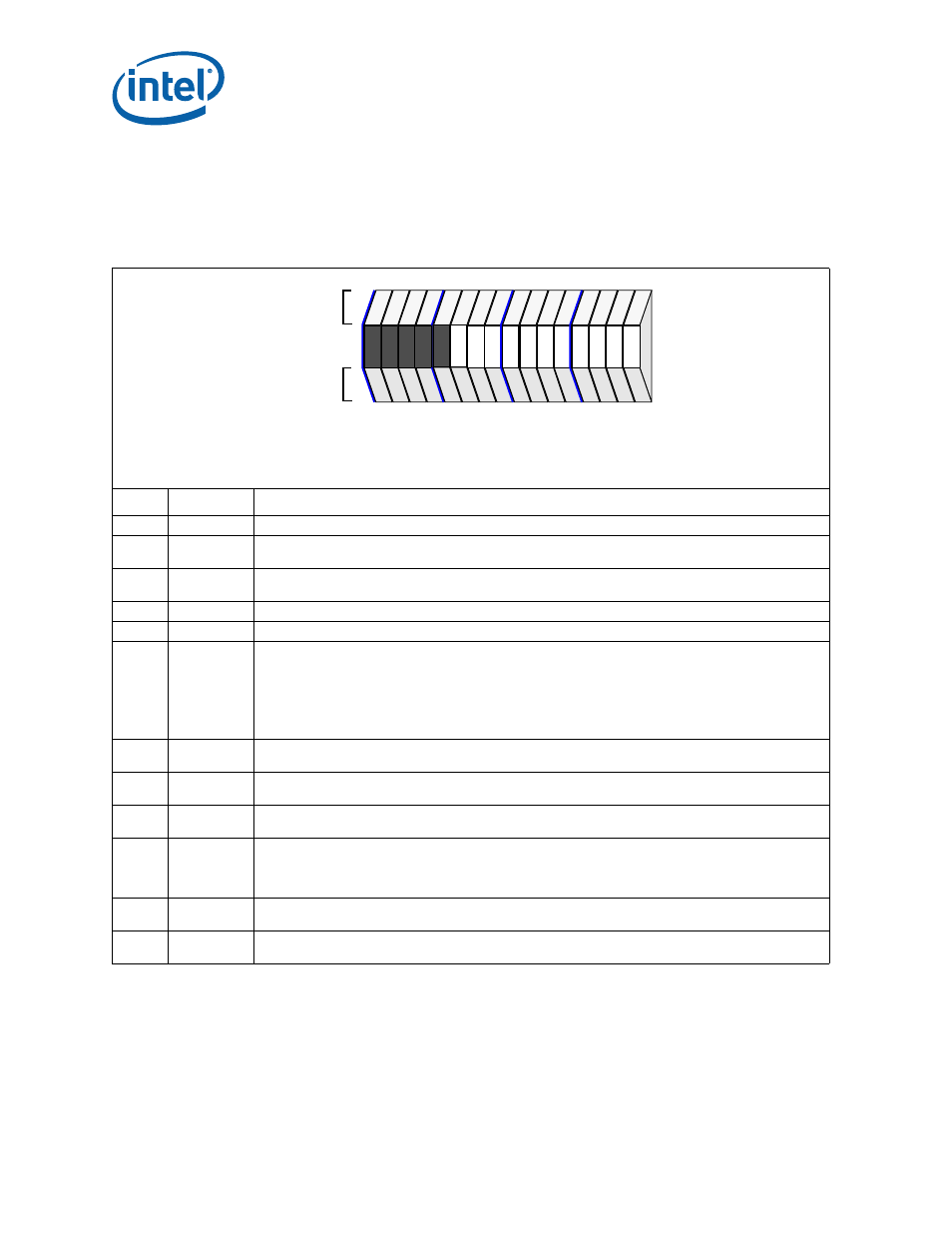

Table 31. ATU Command Register - ATUCMD

Bit

Default

Description

15:11

00000

2

Reserved

10

0

2

Interrupt Disable - Setting this bit disables the ATU function of 4138xx from asserting the

INT[A:D]#

signals. Clearing this bit enables the assertion of the

INT[A:D]#

signals by the ATU function of 4138xx.

09

0

2

Fast Back to Back Enable - When cleared, the ATU interface is not allowed to generate fast back-to-back

cycles on its bus. Ignored when operating in the PCI-X mode.

08

0

2

SERR#

Enable - When cleared, the ATU interface is not allowed to assert

SERR#

on the PCI interface.

07

0

2

Hard-wired 0

06

0

2

Parity Error Response - When set, the ATU takes normal action when a parity (or uncorrectable ECC)

error is detected. When cleared, parity (or uncorrectable ECC) checking is disabled.

Note:

When the bit is cleared in PCI-X Mode 2, the 4138xx records all ECC errors in the ECC Control

and Status, ECC First Address, ECC Second Address, and ECC Attribute registers but in all other

respects treats the transaction as though it had no error. Correctable ECC errors are corrected

independent of the state of this bit.

05

0

2

VGA Palette Snoop Enable - The ATU interface does not support I/O writes and therefore, does not

perform VGA palette snooping.

04

0

2

Memory Write and Invalidate Enable - When set, ATU may generate MWI commands. When clear, ATU

use Memory Write commands instead of MWI. Ignored when operating in the PCI-X mode.

03

0

2

Special Cycle Enable - The ATU interface does not respond to special cycle commands in any way. Not

implemented and a reserved bit field.

02

0

2

Bus Master Enable - The ATU interface can act as a master on the PCI bus. When cleared, disables the

device from generating PCI accesses. When set, allows the device to behave as a PCI bus master.

When operating in the PCI-X mode, ATU initiates a split completion transaction regardless of the state of

this bit.

01

0

2

Memory Enable - Controls the ATU interface’s response to PCI memory addresses. When cleared, the

ATU interface does not respond to any memory access on the PCI bus.

00

0

2

I/O Space Enable - Controls the ATU interface response to I/O transactions.

The ATU does not support I/O transactions. This bit is Read Only.

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

ro

ro

rw

rw

ro

ro

rw

rw

ro

ro

rw

rw

rw

rw

ro

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+004H