1 interrupt base register - intbase, Table 383. interrupt base register - intbase, 1 interrupt base register — intbase – Intel CONTROLLERS 413808 User Manual

Page 583: 383 interrupt base register — intbase, Table 383. interrupt base register — intbase, Interrupt controller unit—intel, Bit default description, Intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

583

Interrupt Controller Unit—Intel

®

413808 and 413812

10.7.1

Interrupt Base Register — INTBASE

The Interrupt Base Register indicates the beginning of the Interrupt Service Routine

(ISR) memory range that contains the interrupt service routines for up to 128 sources.

The starting address must be on a boundary equal to the granularity of the ISR

memory range as specified by the INTSIZE registers.

For instance, the upper 23 bits are used for a 512 Byte ISR memory range, and the

upper 16 bits for a 64 KByte ISR memory range., etc.

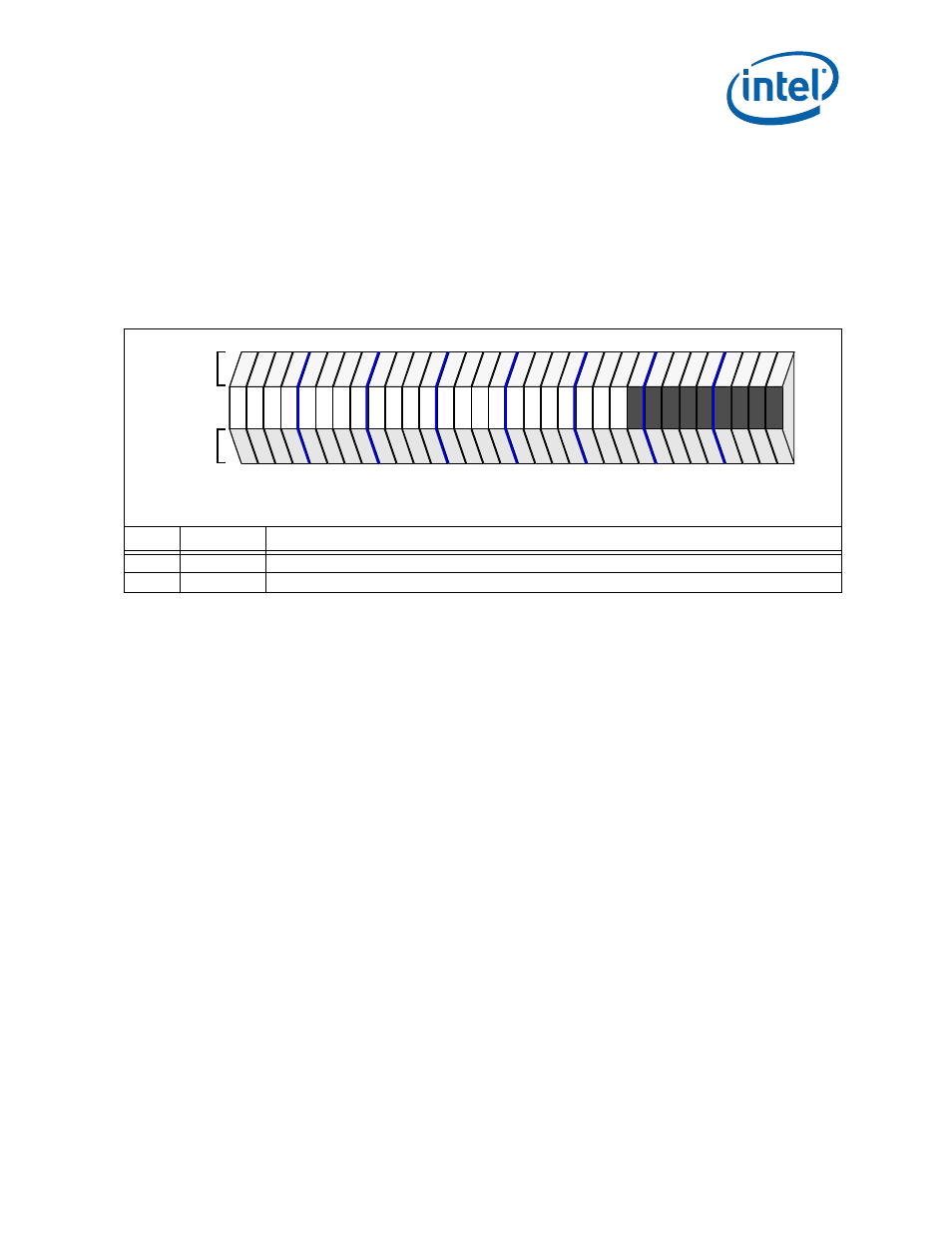

Table 383. Interrupt Base Register — INTBASE

Bit

Default

Description

31:09

0000 00H Interrupt Base — These bits define the upper 23 bits of the base address for the ISR memory range.

08:00

00H

Reserved

Memory

Coprocessor

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rw

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor address

CP6, Page 2, Register 0