40 atu configuration register - atucr, Table 67. atu configuration register - atucr, 40atu configuration register - atucr – Intel CONTROLLERS 413808 User Manual

Page 177: 67 atu configuration register - atucr, Section 2.14.40, “atu configuration register, Section, Section 2.14.40, “atu configuration, P_serr, Manual assertion, Address translation unit (pci-x)—intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

177

Address Translation Unit (PCI-X)—Intel

®

413808 and 413812

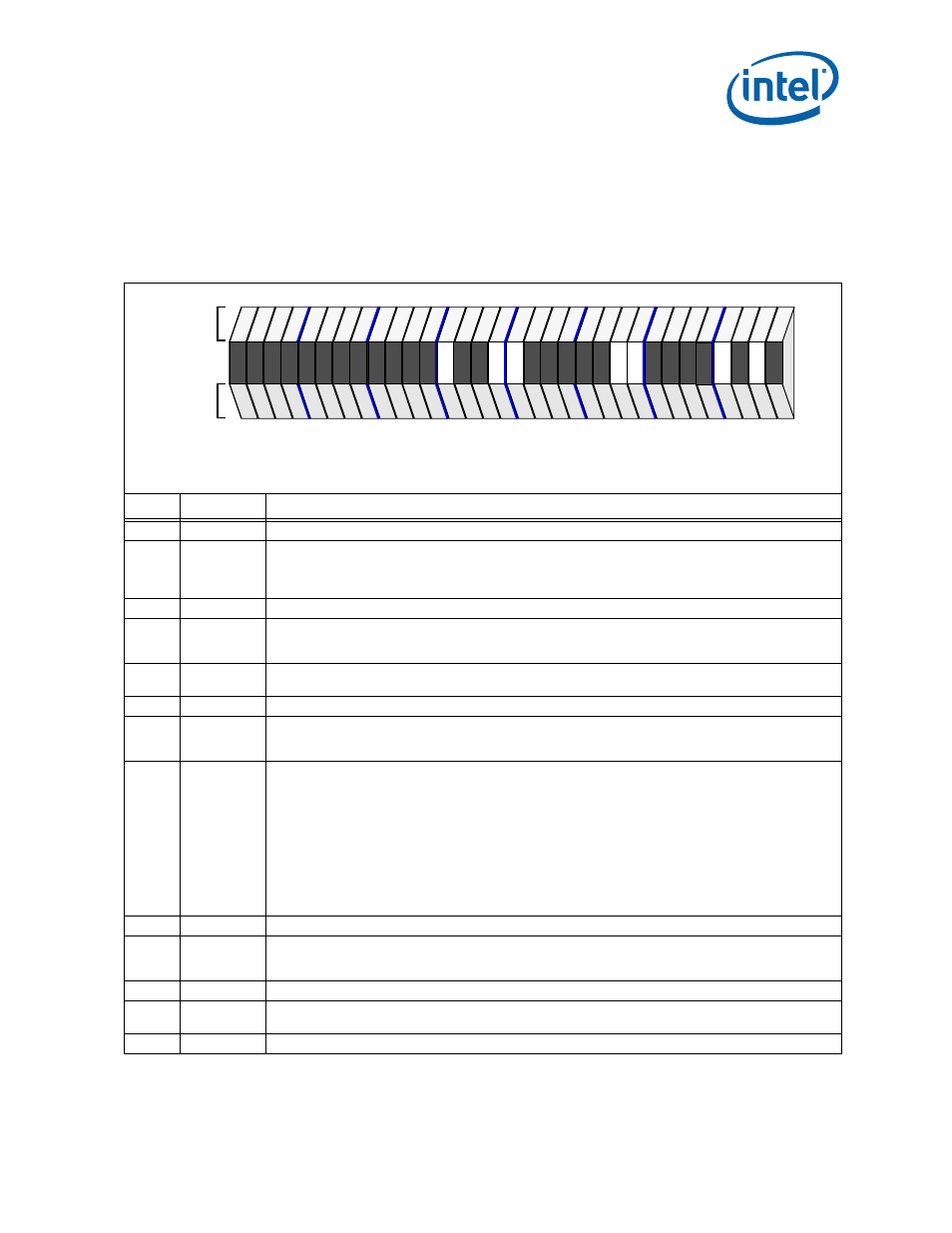

2.14.40 ATU Configuration Register - ATUCR

The ATU Configuration Register controls the outbound address translation for address

translation unit. It also contains bits for Conventional PCI Delayed Read Command

(DRC) aliasing, discard timer status,

P_SERR#

manual assertion,

P_SERR#

detection

interrupt masking, and ATU BIST interrupt enabling.

Table 67. ATU Configuration Register - ATUCR

Bit

Default

Description

31:20

00H

Reserved

19

0

2

ATU DRC Alias - when set, the ATU does not distinguish read commands when attempting to match a

current PCI read transaction with read data enqueued within the DRC buffer. When clear, a current read

transaction must have the exact same read command as the DRR for the ATU to deliver DRC data. Not

applicable in the PCI-X mode.

18:17

00b

Reserved

16

0

2

P_SERR#

Manual Assertion - when set, the ATU asserts

P_SERR#

for one clock on the PCI interface.

Until cleared,

P_SERR#

may not be manually asserted again. Once cleared, operation proceeds as

specified.

15

0

2

ATU Discard Timer Status - when set, one of the 4 discard timers within the ATU has expired and

discarded the delayed completion transaction within the queue. When clear, no timer has expired.

14:10

00

2

Reserved

09

0

2

P_SERR#

Detected Interrupt Enable - When set, the Intel XScale

®

processor is signalled an

HPI#

interrupt when the ATU detects that

P_SERR#

was asserted. When clear, the Intel XScale

®

processor

is not interrupted when

P_SERR#

is detected.

08

0

2

Halt ATU On Error Enable - When set and a Data Parity, Master-Abort, or Target-Abort error occurs on

an Outbound PCI Write Request, the ATU halts operation using the following sequence:

1.

Stop accepting Outbound Requests by clearing the Outbound ATU Enable (bit 1 of the ATUCR).

2.

Flush any pending outbound write requests from the transaction queue.

3.

Pull the Intel XScale

®

processor interrupt as normal for the error.

Firmware should wait for the Outbound Queue Busy Bit in

“PCI Configuration and Status Register -

to clear before setting the Outbound ATU Enable (ATUCR[1]).

Note:

Due to the pipelined nature of PERR# signaling, one additional write may have issued on the

PCI bus before the error condition is detected. All remaining writes in the queue is flushed.

Read Requests are allowed to proceed and complete normally though no new ones are accepted.

07:04

000

2

Reserved

03

0

2

ATU BIST Interrupt Enable - When set, enables an interrupt to the Intel XScale

®

processor when the

start BIST bit is set in the ATUBISTR register. This bit is also reflected as BIST Capable bit 7 in the

ATUBISTR register.

02

0

2

Reserved

01

0

2

Outbound ATU Enable - When set, enables the outbound address translation unit. When cleared,

disables the outbound ATU.

00

0

2

Reserved

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rv

rv

rv

rv

rw

rw

rc

rc

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rv

rv

rw

rw

rv

rv

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Register Offset

+070H