1 normal interrupt sources, Table 379. normal interrupt sources, 379 normal interrupt sources – Intel CONTROLLERS 413808 User Manual

Page 577

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

577

Interrupt Controller Unit—Intel

®

413808 and 413812

10.5.3.1 Normal Interrupt Sources

The 4138xx Interrupt Controller receives normal interrupts from the Application DMA

channels, Performance Monitoring Unit, the I

2

C Bus Interface Unit, the ATUE, the ATUX,

the Programmable Timers, the Messaging Unit and the UARTs. The Application DMA

channel interrupts for End of Transfer interrupt or End of Chain interrupt are

demultiplexed into the interrupt controller.

A valid interrupt from any of these sources outputs a level-sensitive interrupt to the

4138xx Interrupt Controller input. The corresponding IRQ or FIQ interrupt source

register bit in the interrupt controller should remain active as long as the interrupt is

pending in the peripheral unit. The appropriate interrupt source bit is cleared by

clearing the source of the interrupt at the internal peripheral.

The normal interrupt sources which drive the inputs to the 4138xx Interrupt Controller

are detailed in

.

Note:

The UART and I

2

C Bus Interface Unit interrupt sources are combined as a single

interrupt, and include both normal and error conditions within the respective units.

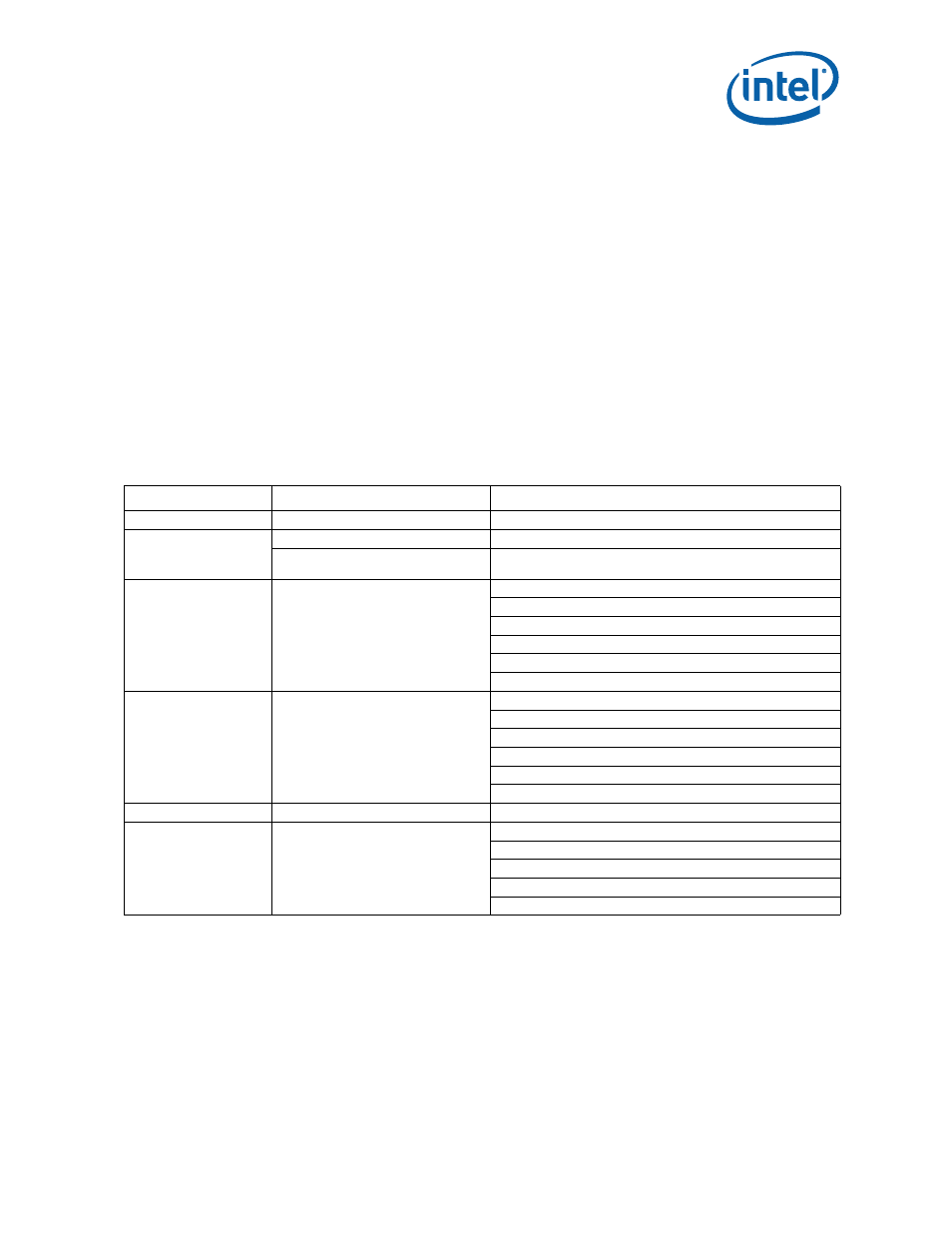

Table 379. Normal Interrupt Sources

Unit

Register

Interrupt Condition

Intel XScale

®

processor Overflow Flag Status Register (FLAG) Counter Overflow

ATU -X & -E

ATU -X & -E Interrupt Status Register ATU BIST Start

Configure Reg Write

Any of the ATU Configuration registers written by an inbound

Configuration Write cycle

I

2

C Bus Interface Unit

2-0

I

2

C Status Register 2-0

Receive Buffer Full

Transmit Buffer Empty

Slave Address Detect (General Call Address Detect)

STOP Detected

Bus Error Detected

Arbitration Lost Detected

Messaging Unit

Inbound Interrupt Status Register

Inbound Doorbell Interrupt

Inbound Message 1 Interrupt

Inbound Message 0 Interrupt

MU MSI-X Table Write Interrupt

Selective Reset Interrupt

Coordinated Reset Interrupt

Timer 1 & 0

Timer Mode Register 1 & 0

Timer 0 has decremented to 0 interrupt.

UART Unit 1 & 0

UART 1 & 0 Interrupt ID Register

Received Line Status

Received Data is Available

Character Time-out Indications

Transmit FIFO Data Request

Autobaud Lock Indication