Pci express advisory error, Control register - pie_aec, Pci express advisory error control register – Intel CONTROLLERS 413808 User Manual

Page 366: Pie_aec, Express advisory error control register - pie_aec, Pci express, Advisory error control register - pie_aec, Intel, Bit default description

Intel

®

413808 and 413812—Address Translation Unit (PCI Express)

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

366

Order Number: 317805-001US

3.17.86 PCI Express Advisory Error Control Register - PIE_AEC

This registers enables Advisory Error functionality for devices that attempts to recover

from certain errors. Firmware can attempt to recover from these non-fatal conditions

zero, once, or more (finite) times. Once the retry limit has been reached the generate

ERR_NONFATAL bit should be set to alert the host to problem.

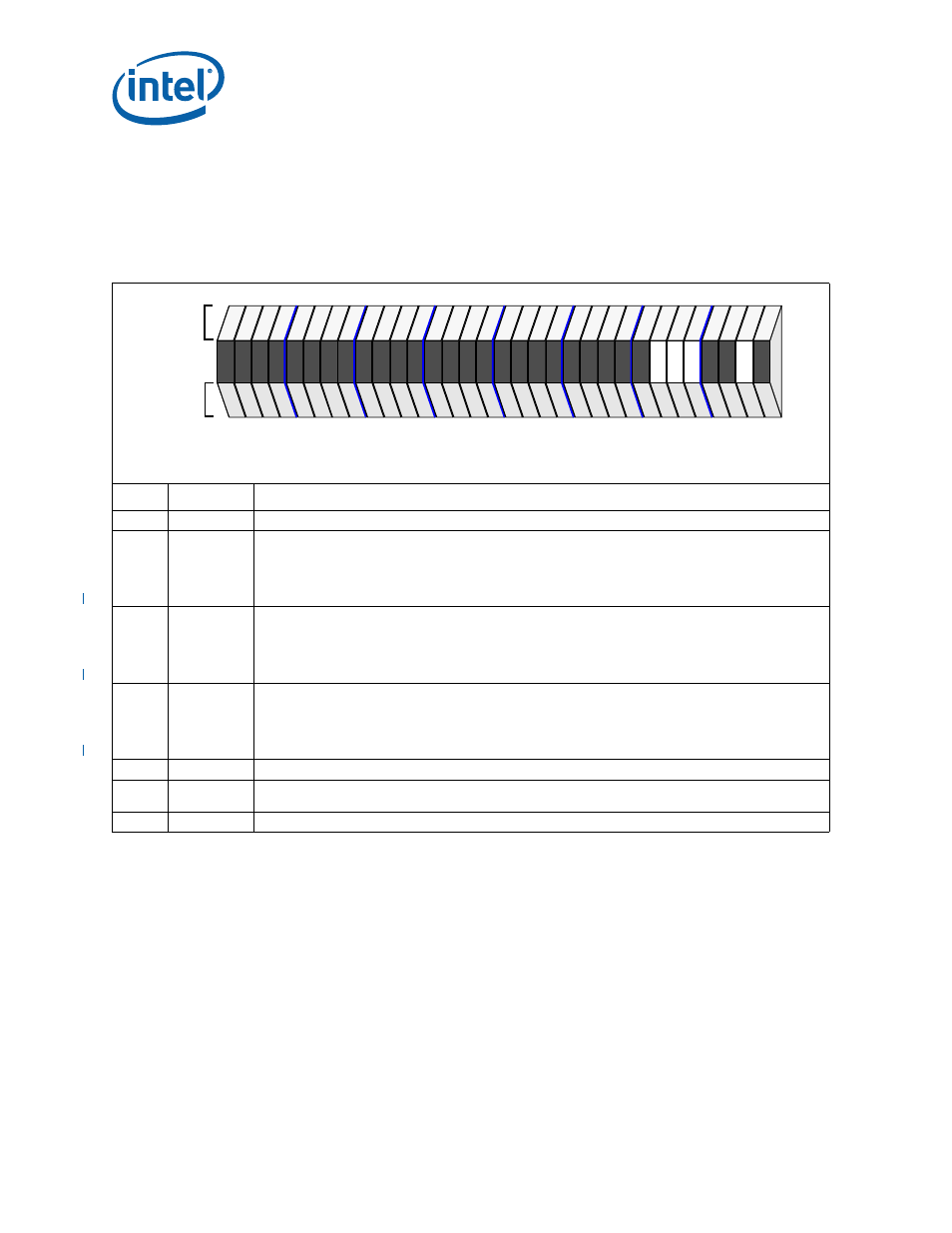

Table 226. PCI Express Advisory Error Control Register PIE_AEC

Bit

Default

Description

31:07

0

Reserved

6

0

Advisory Error Enable for Completion Timeout - This bit determines the behavior when detecting a

completion timeout.

0 = Do not treat as an Advisory Error. Send ERR_NONFATAL to root complex when error is detected

1 = Treat as Advisory Error and send ERR_COR to root complex

See

Section 3.9.1.8, “Completion Timeout” on page 274

for more details.

5

0

Advisory Error Enable for Poisoned Posted TLPs - This bit determines the behavior when receiving a

posted transaction that has poisoned data.

0 = Do not treat as an Advisory Error. Send ERR_NONFATAL to root complex when error is detected

1 = Treat as Advisory Error and send ERR_COR to root complex

See

Section 3.9.1.7, “Poisoned TLP Received” on page 274

4

0

Advisory Error Enable for Poisoned Completions - This bit determines the behavior when receiving a

completion transaction that has poisoned data.

0 = Do not treat as an advisory error. Send ERR_NONFATAL to root complex when error is detected

1 = Treat as Advisory Error and send ERR_COR to root complex

See

Section 3.9.1.7, “Poisoned TLP Received” on page 274

3:2

00

Reserved

1

0

Generate ERR_NONFATAL - When asserted an ERR_NONFATAL message is sent to the root complex. This

bit is self-clearing and always returns zero when read.

0

0

Reserved

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rv

rv

rv

rv

rw

rw

rv

rv

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+1ECH