Address translation unit (pci express)—intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 377

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

377

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.98 Outbound Upper Memory Window Base Address Register 2 -

OUMBAR2

The OUMBAR2 register locates Outbound Memory Window 2 in a 4 Gbyte Memory

section in the 4138xx’s 64 Gbyte internal address space. When A[35:32] of the internal

bus address matches the value in OUMBAR2[3:0], the ATU claims the transaction and

forward it over to the PCI interface.

Note:

In translating the internal bus address A[35:0], A[31:0] is forwarded over to the PCI

bus unmodified. The ATU constructs a 64 bit PCI address in conjunction with the

“Outbound Upper 32-bit Memory Window Translate Value Register 2 - OUMWTVR2” on

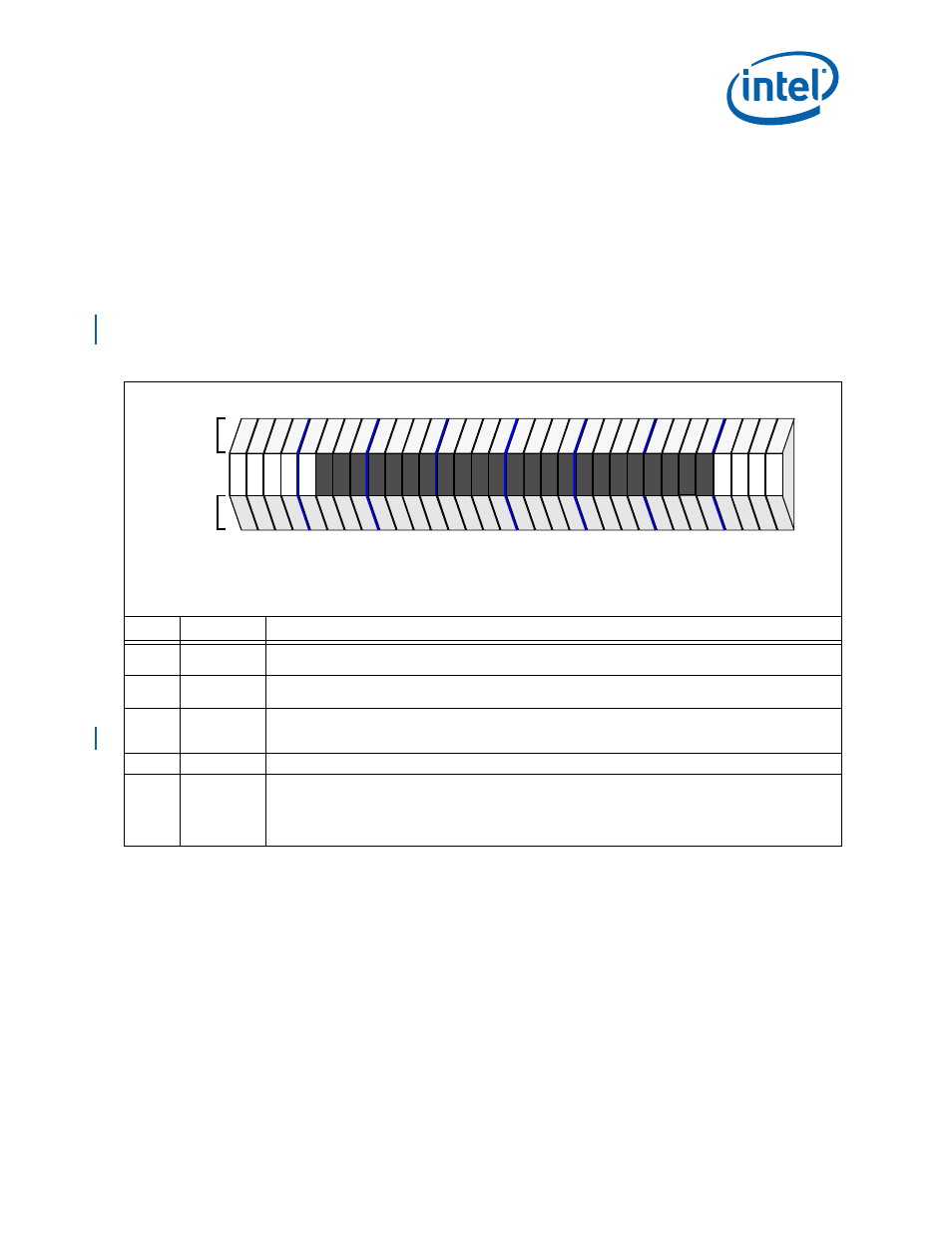

Table 238. Outbound Upper Memory Window Base Address Register 2- OUMBAR2

Bit

Default

Description

31

0

2

Outbound Window 2 Enable - When set, the ATU Outbound Memory Window 2 claims internal bus

transactions when A[35:32] matches OUMBAR2[3:0].

30:28

000

2

Outbound Window 2 Function Number Mapping - Errors with Outbound Memory Window 2 transactions

(PCI or Internal Bus) are associated with the function number contained in this field.

27

0

Big Endian Byte Swap enable - When set the ATU performs a byte swap on all read/write transactions

through this BAR. When clear, no swap is performed. Refer to

Section 3.4, “Big Endian Byte Swapping”

for more details.

26:04

000 0000H Reserved

3:0

3H

Outbound Upper Memory Window Base Address 2 - This value represents bits 35 to 32 of the internal

bus address used to claim an outbound memory request.

Note:

The ATUX has the same default value. When both ATUs exist and the outbound windows of the

both ATUs are enabled, the bit field must be reprogrammed to avoid a conflict.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

rw

rw

rw

rw

rw

rw

rw

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+318H