Intel, Bit default description – Intel CONTROLLERS 413808 User Manual

Page 420

Intel

®

413808 and 413812—Messaging Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

420

Order Number: 317805-001US

4.7.10

Outbound Reset Control and Status Register - ORCSR

The Outbound Reset Control and Status Register (ORCSR) provides the ability for the

I/O-processor to coordinate a hardware reset with the Host processor when

multi-function is being used. In a multi-function scenario, before the Host driver can

issue a hardware reset via one of the functions, all the host drivers running must be

quiesced.

Note:

GRO and RM bits of the ORCSR are saved in the Reset Cause Status Register (RCSR)

when both CR and SR bits of the IRCSR are set to cause an internal bus reset. The

Reset Cause Status Register implements sticky bits. The initiator of the internal bus

reset is also indicated in the RCSR. Refer to the

Exception Initiator and Boot Sequence

Chapter

for detailed descriptions of the RCSR register.

Table 275. Outbound Reset Control and Status Register - ORCSR

Bit

Default

Description

31

0

2

Firmware Interrupt - This bit is set by the firmware to initiate an interrupt to the Host processor and this

bit is used during a coordinated reset handshaking sequence. Firmware sets this bit. The host clears this

bit by writing a 1.

30:04

00000H

Reserved.

03

0

2

Global Reset Outstanding (GRO) - This bit is only used when the 4138xx

implements Multi-Function

Reset protocol (MF=1, bit 1 in the ORCSR). When the Host Processor request a coordinated reset in one

of the Function Interfaces, and the 4138xx implements Multi-function Reset protocol, the 4138xx

firmware sets the GRO bit on all function interfaces. When Multi-Function Reset protocol is not

implemented, this bit is always zero.

Note:

The state of this bit is saved in the Reset Cause Status Register (RCSR) when an internal bus

reset occurs. Refer to the

Exception Initiator and Boot Sequence Chapter

for detailed

descriptions of the RCSR register.

02

0

2

Reset Coordination Complete (RCC) - This bit is used during a Coordinated Reset to indicate to the Reset

Master that all the other Host Drivers have acknowledged the pending reset and that the Reset Master

may proceed with the reset. The Coordinated Reset is only available on 4138xx that implement the

Multi-function Feature (MF=1, bit 1 in the ORCSR). This bit is only set by the Core when GRO and RM

are both set.

01

0

2

Multi-Function (MF) - The Intel XScale

®

processor sets this bit to indicate that the 4138xx supports

multiple PCI function features such as multi-function reset.

00

0

2

Reset Master (RM) - This bit is set by firmware when one of the Host drivers requests a Coordinated

Reset and this Interface takes on the Reset Master role during the Coordinated Reset. This feature is

only available when the MF bit is set, bit 1 in the ORCSR. The Host driver requests a Coordinated Reset

by writing a 1 into the CR bit, bit 1 of the IRCSR.

Note:

The state of this bit is saved in the Reset Cause Status Register (RCSR) when an internal bus

reset occurs. Refer to the

Exception Initiator and Boot Sequence Chapter

for detailed

descriptions of the RCSR register.

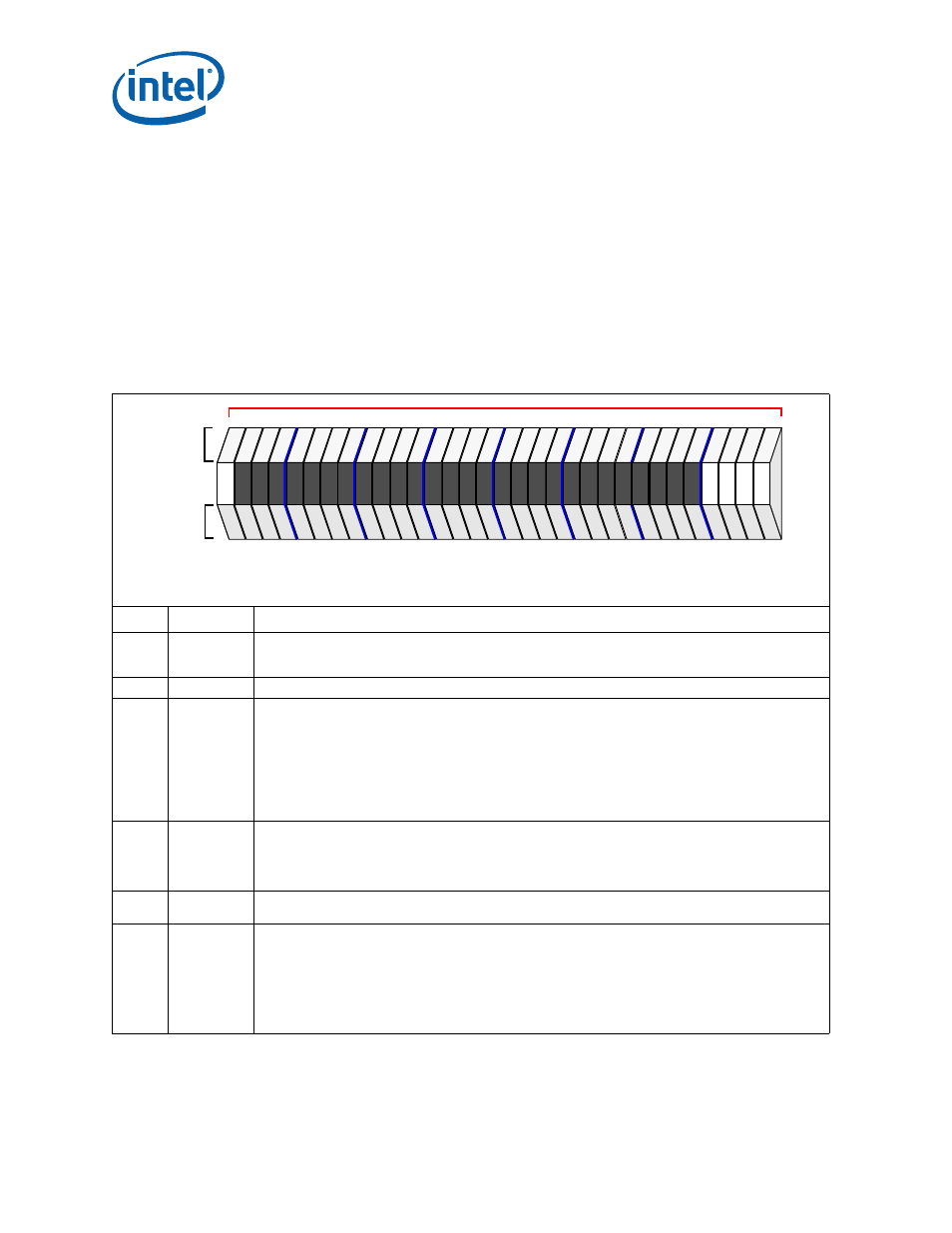

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rs

rc

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rv

rw

ro

rw

ro

rw

ro

rw

ro

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

MU/PCI Base Address Offset

OIMR: 003CH

internal bus address offset

OIMR: 403CH