63 pci express link status register - pe_lsts, 63pci express link status register - pe_lsts, 203 pci express link status register pe_lsts – Intel CONTROLLERS 413808 User Manual

Page 349: Pci express link status register, Pe_lsts, Address translation unit (pci express)—intel, Bit default description

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

349

Address Translation Unit (PCI Express)—Intel

®

413808 and 413812

3.17.63 PCI Express Link Status Register - PE_LSTS

This register controls various modes and features of ATU and Message Unit when

operating in the PCI Express mode.

Table 203. PCI Express Link Status Register PE_LSTS

Bit

Default

Description

15:13

0H

Reserved

12

1

Slot Clock Configuration - Indicates that the component uses the same physical reference clock that the

platform provides on the connector.

This bit must be cleared when the device uses an independent reference clock.

11

0

Link Training -

As an endpoint, this bit is hard-wired to 0

For root complex, this read-only bit indicates that Link training is in progress.

Hardware clears this bit once Link training is complete.

10

0

Link Training Error -

As an endpoint, this bit is hard-wired to 0

For root complex, this read-only bit indicates that a Link training error occurred.

This bit is cleared by hardware upon successful training of the Link to L0 link state.

9:4

00H

Negotiated Link Width - Defined encodings are

01H x1

02H x2

04H x4

08H x8

12H x12 (Unsupported)

10H x16 (Unsupported)

20H x32 (Unsupported)

All other encodings are reserved

3:0

1H

Link Speed - Negotiated Link Speed.

1H indicates 2.5Gb/s Link speed. All other encodings are reserved.

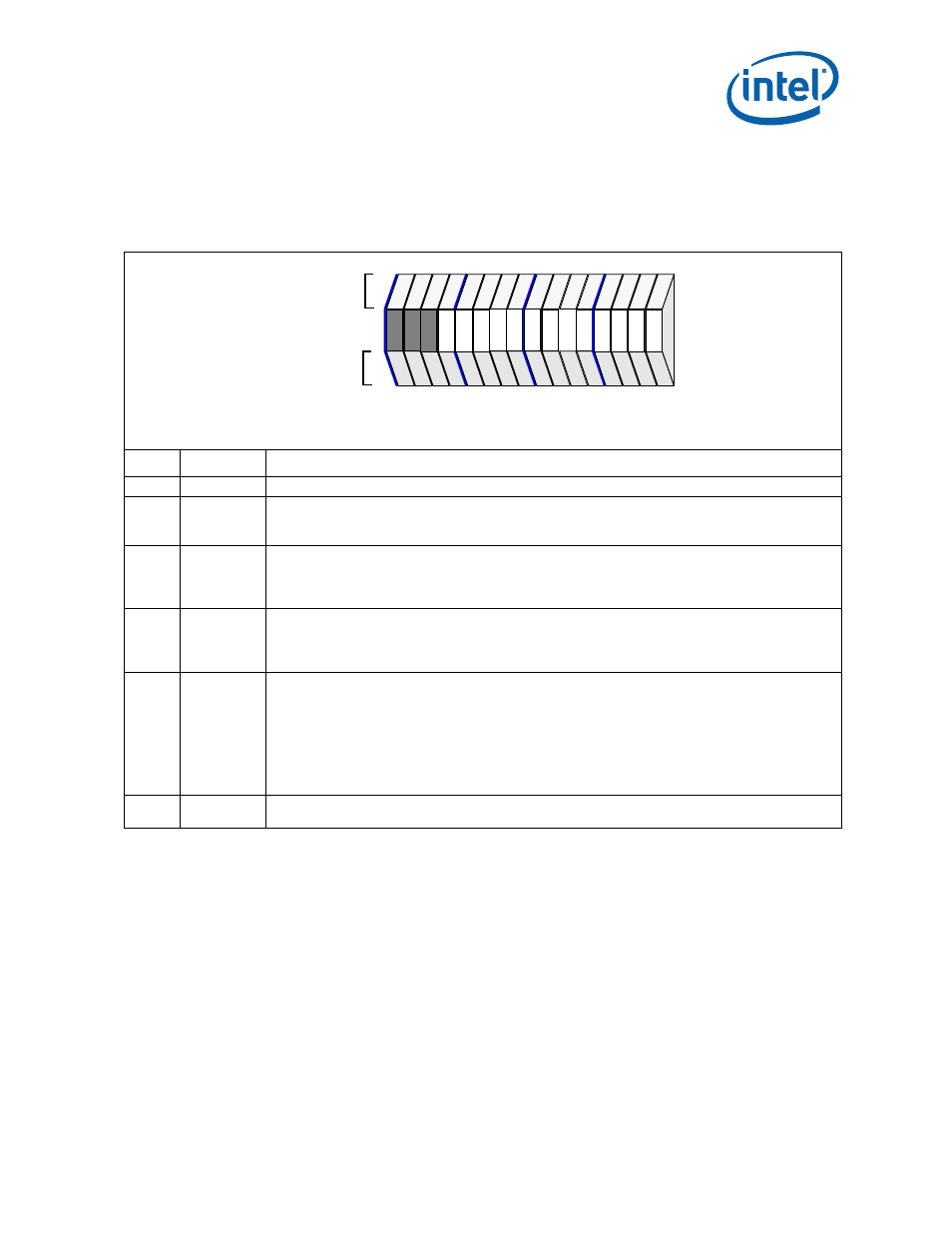

PCI

IOP

Attributes

Attributes

15

12

8

4

0

rz

rz

rz

rz

rz

rz

rw

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

ro

Attribute Legend:

RZ = Reserved Zero

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal Bus Address Offset

+0E2H