2 system controller, Table 526. sc base address offset, Table 527. system controller unit – Intel CONTROLLERS 413808 User Manual

Page 802: 3 internal bus bridge, Table 528. internal bus bridge base address offset, Table 529. internal bus bridge, 526 sc base address offset, 527 system controller unit, 528 internal bus bridge base address offset, 529 internal bus bridge

Intel

®

413808 and 413812—Peripheral Registers

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

802

Order Number: 317805-001US

19.6.1.2 System Controller

The System Controller Unit (SC) is allocated 16 Bytes of PMMR register space and is

always located at offset +1640H relative to the PMMRBAR.

Use the following equation to calculate the actual register address:

Internal Bus Address = PMMRBAR + SC Base Address Offset + Register Offset.

19.6.1.3 Internal Bus Bridge

The Internal Bus Bridge is allocated 24 Bytes of PMMR register space and is always

located at offset +1780H relative to the PMMRBAR.

Use the following equation to calculate the actual register address:

Internal Bus Address = PMMRBAR + Internal Bus Bridge Address Offset + Register

Offset.

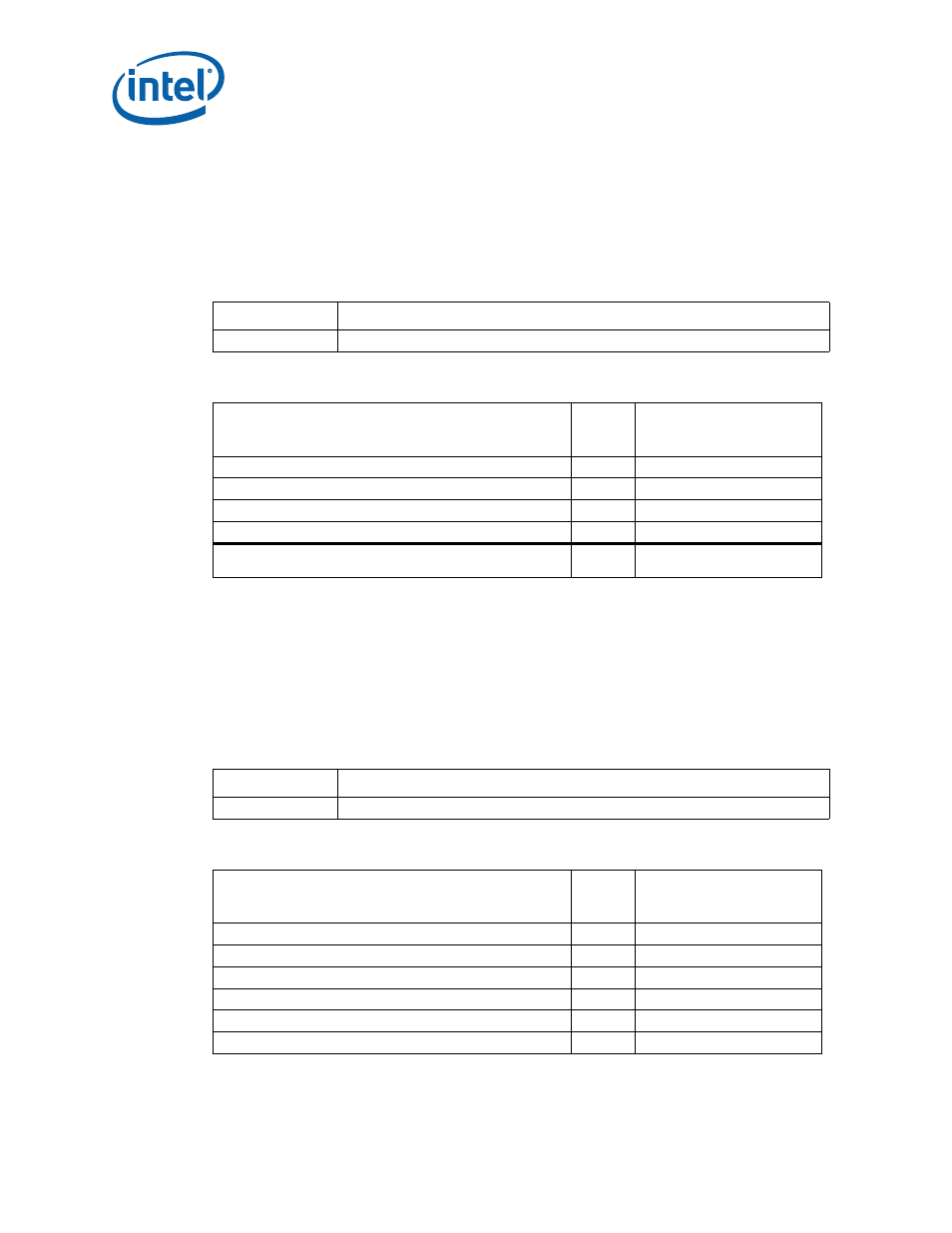

Table 526. SC Base Address Offset.

Unit

SC Base Address Offset (Relative to PMMRBAR)

System Controller

+1640H

Table 527. System Controller Unit

Register Description (Name)

Register

Size in

Bits

Internal Bus Address Offset

(Relative to SC Base

Address Offset)

Internal Bus Arbitration Control Register — IBACR

32

+00H

South Internal Bus Address Test Register — SIBATCR

32

+04H

South Internal Bus Data Test Register — SIBDTCR

32

+08H

Reserved

x

+0CH through 0FH

Peripheral Memory-Mapped Register Base Address Register

(PMMRBAR)

32

F FFFF FFFCH

(

absolute address

)

Table 528. Internal Bus Bridge Base Address Offset.

Unit

Internal Bus Bridge Base Address Offset (Relative to PMMRBAR)

Internal Bus Bridge

+1780H

Table 529. Internal Bus Bridge

Register Description (Name)

Register

Size in

Bits

Internal Bus Address Offset

(Relative to Internal Bus

Bridge Base Address Offset)

Bridge Window Base Address Register — BWBAR

32

+00H

Bridge Window Upper Base Address Register — BWUBAR

32

+04H

Bridge Window Limit Register — BWLR

32

+08H

Bridge Error Status Register — BECSR

32

+0CH

Bridge Error Address Register — BERAR

32

+10H

Bridge Error Upper Address Register — BERUAR

32

+14H