Intel – Intel CONTROLLERS 413808 User Manual

Page 574

Intel

®

413808 and 413812—Interrupt Controller Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

574

Order Number: 317805-001US

The INTBASE and INTSIZE registers are used to establish a contiguous Interrupt

Service Routine (ISR) memory range for all of 128 possible sources. The architecture

provides for an ISR ranging from 4 bytes to 64 Kbytes per source.

The actual vector value is a function of the INTBASE and the INTSIZE registers and is

based on a fixed order of all 128 possible interrupt sources. The vectors begin at

INTBASE with source 0 (i.e., IINTSRC0 bit 0), and end at INTBASE + INTSIZE (per

source) × 127 with source 127 (that is, IINTSRC3 bit 31).

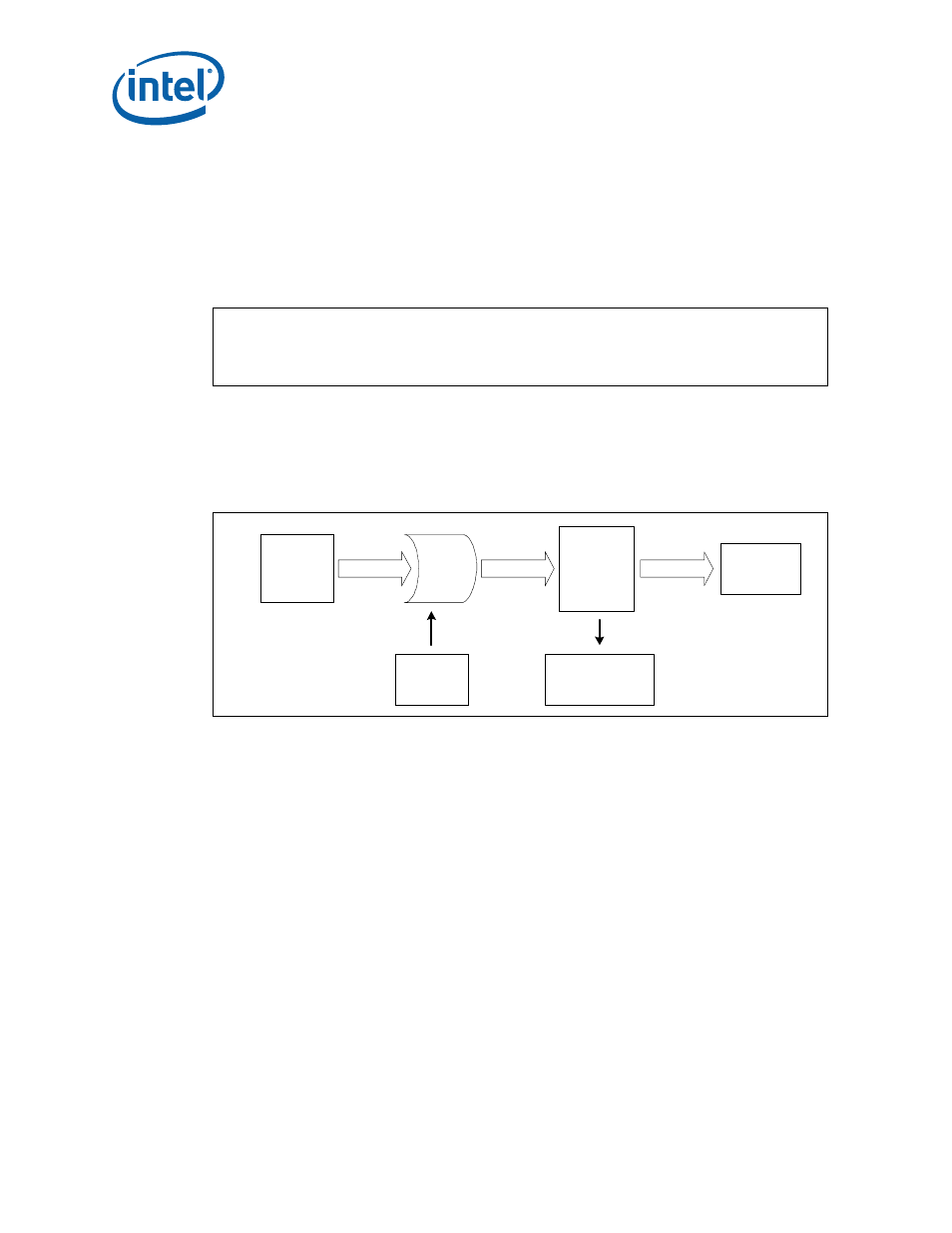

Based on IINTSRC[3:0], FINTSRC[3:0], IPR[7:0], INTBASE, and INTSIZE, the interrupt

controller generates the values provided by the IINTVEC and FINTVEC registers as

illustrated in

. The IINTVEC and FINTVEC registers present the vector for the

active interrupt source with the highest priority to the IRQ and FIQ exception handlers,

respectively.

Note:

The 4138xx does not use all 128 possible sources.

ICU registers reside in Coprocessor 6 (CP6). They may be accessed/manipulated with

the MCR, MRC, STC, and LDC instructions. The instruction CRn field denotes the

accessed register number. The instruction opcode_1, opcode_2, and CRm fields should

be zero. Most systems restrict access to CP6 to privileged processes. To control access

to CP6, use Coprocessor Access Register.

An instruction that modifies an ICU register is insured to take effect before the next

instruction executes. For example, when an instruction masks an interrupt source,

subsequent instructions execute in an environment in which the masked interrupt does

not occur.

Example 6. Determining the Location of the Interrupt Handler for Source 25

INTBASE = 0x81400000 ; 4 Mbyte Aligned Base Address

INTSIZE = 0xE ; 32 Kbytes per source (ISR Memory Range of 4 Mbytes)

ISR Address(25) = 0x81400000 + conv_hex(2^15*25) = 0x814C8000

Figure 69. Interrupt Controller Block Diagram (FIQ/IRQ Interrupt Vector Generation)

Prioritizer

128- bit

128- bit

Interrupt

Source

Registers

(FIQ or IRQ )

Interrupt

Priority

Registers

[0:7]

Vector

Generator

32- bit

INTSRC ( x)

Vector = INTBASE

Register +

INTSIZE Register *x

FIQ or IRQ

Interrupt

Vector

Register

B6273-01