102 master-transmitter write to slave-receiver, 103 master-receiver read to slave-transmitter, Slave-receiver706 – Intel CONTROLLERS 413808 User Manual

Page 706: Intel, C bus interface units

Intel

®

413808 and 413812—I

2

C Bus Interface Units

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

706

Order Number: 317805-001US

through

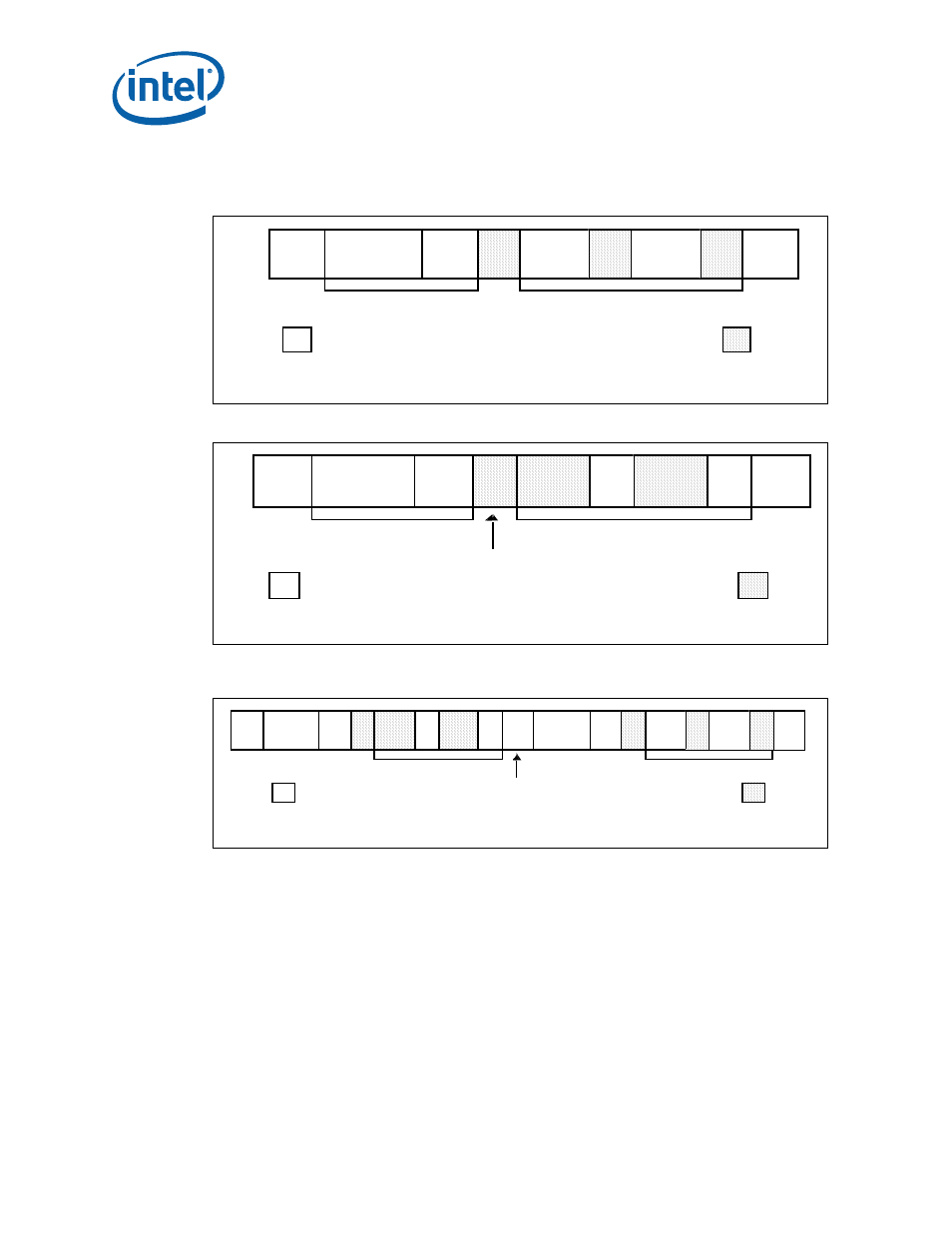

are examples of I

2

C transactions. These show the

relationships between master and slave devices.

Figure 102. Master-Transmitter Write to Slave-Receiver

Figure 103. Master-Receiver Read to Slave-Transmitter

Figure 104. Master-Receiver Read to Slave-Transmitter, Repeated START,

Master-Transmitter Write to Slave-Receiver

Master to Slave

Slave to Master

START

Slave

Address

R/W#

0

ACK

Data

Byte

ACK

Data

Byte

STOP

N Bytes + ACK

Write

ACK

First Byte

B6292-01

Master to Slave

Slave to Master

START

Slave

Address

R/W#

1

ACK

Data

Byte

ACK

Data

Byte

STOP

N Bytes + ACK

Read

ACK#

Default

Slave-Receive

Mode

First Byte

B6293-01

S

TA

R

T

R

/W

#

1

Data

Byte

Data

Byte

N Bytes + ACK

Read

SR

R

/W

#

0

Data

Byte

Data

Byte

S

TO

P

N Bytes + ACK

Write

Slave

Address

Master to Slave

Slave to Master

Repeated

START

Data Chaining

A

C

K

A

C

K

A

C

K

A

C

K

A

C

K

Slave

Address

A

C

K

B6294-01