Figure 40. internal bus memory map, Table 264. mu summary, 40 internal bus memory map – Intel CONTROLLERS 413808 User Manual

Page 401: 264 mu summary, Messaging unit—intel, Intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

401

Messaging Unit—Intel

®

413808 and 413812

Note:

See

Table 265, “Message Unit Registers”

for more details.

provides a summary of the two messaging mechanisms used in the

Messaging Unit.

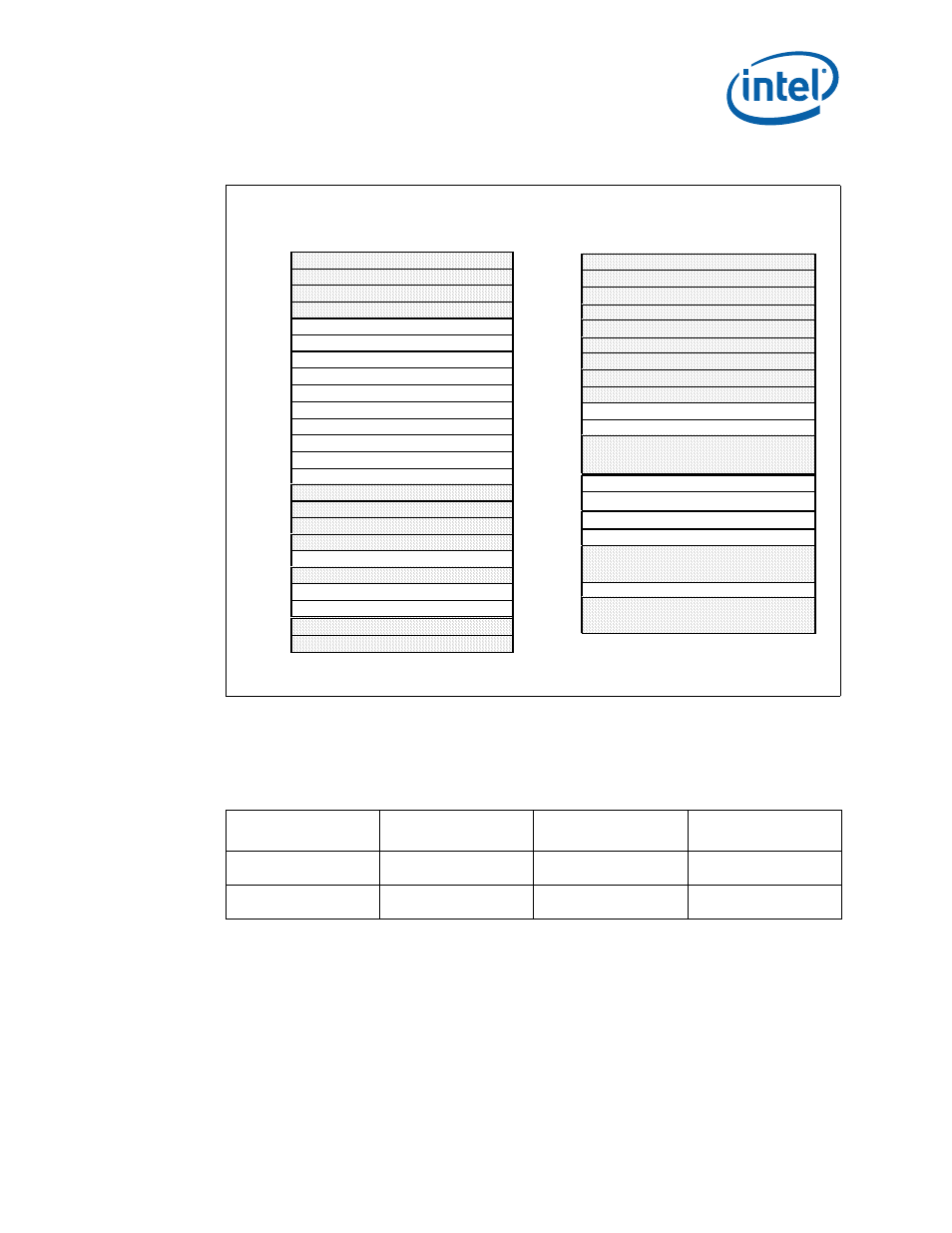

Figure 40. Internal Bus Memory Map

a X is equal to 0H, 1H, 2H, 3H, 4H, 5H, 6H, or 7H

Offsets are relative to the PMMRBAR

Inbound Message Register 0

Inbound Message Register 1

Outbound Message Register 0

Outbound Message Register 1

Inbound Doorbell Register

Inbound Interrupt Status Register

Inbound Interrupt Mask Register

Outbound Doorbell Register

Outbound Interrupt Status Register

Outbound Interrupt Mask Register

Reserved

Reserved

Reserved

Reserved

Reserved

MU Configuration Register

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

MSI Inbound Message Register

4000H

4010H

401CH

4018H

4014H

4020H

4024H

4028H

402CH

4034H

4038H

403CH

4040H

4044H

4048H

404CH

4050H

4030H

405CH

4058H

4054H

Offset

4004H

4008H

400CH

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

MU Base Address Register

MU Upper Base Address Register

MU MSI-X Table Message Address

MU MSI-X Table Message Upper Address

MU MSI-X Table Message Data

MU MSI-X Table Vector Control

MU MSI-X PBA

Reserved

Reserved

Reserved

4060H

4064H

4068H

406CH

4074H

4070H

4078H

407CH

4080H

4084H

4088H

408CH

50X0 aH

50XCaH

50X8 aH

50X4aH

5800H

through

4FFCH

5080H

through

57FCH

5804H

through

5FFCH

B6622-01

Table 264. MU Summary

Mechanism

Quantity

Assert PCI Interrupt

Signals?

Generate 4138xx

Interrupt?

Message Registers

2 Inbound

2 Outbound

Optional

Optional

Doorbell Registers

1 Inbound

1 Outbound

Optional

Optional