3 internal bus addresses, Table 487. pmon register summaries, Pmon – Intel CONTROLLERS 413808 User Manual

Page 745

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

745

PMON Unit—Intel

®

413808 and 413812

16.5.3

Internal Bus Addresses

The Internal Bus Address Offset to PMMRBAR of any

PMON

Register can be derived by

adding the 4 KB address aligned Internal Bus Memory Mapped Register Range Offset

Table 486, “PMON Internal Bus Memory Mapped Register Range Offsets” on page 745

)

to the Register Offset (

Table 487, “PMON Register Summaries” on page 745

)

For example the offset to PMMRBAR of the

“PMON Status Register - PMONSTAT”

would be

(4 E000H+044H) or 4 E044H.

T

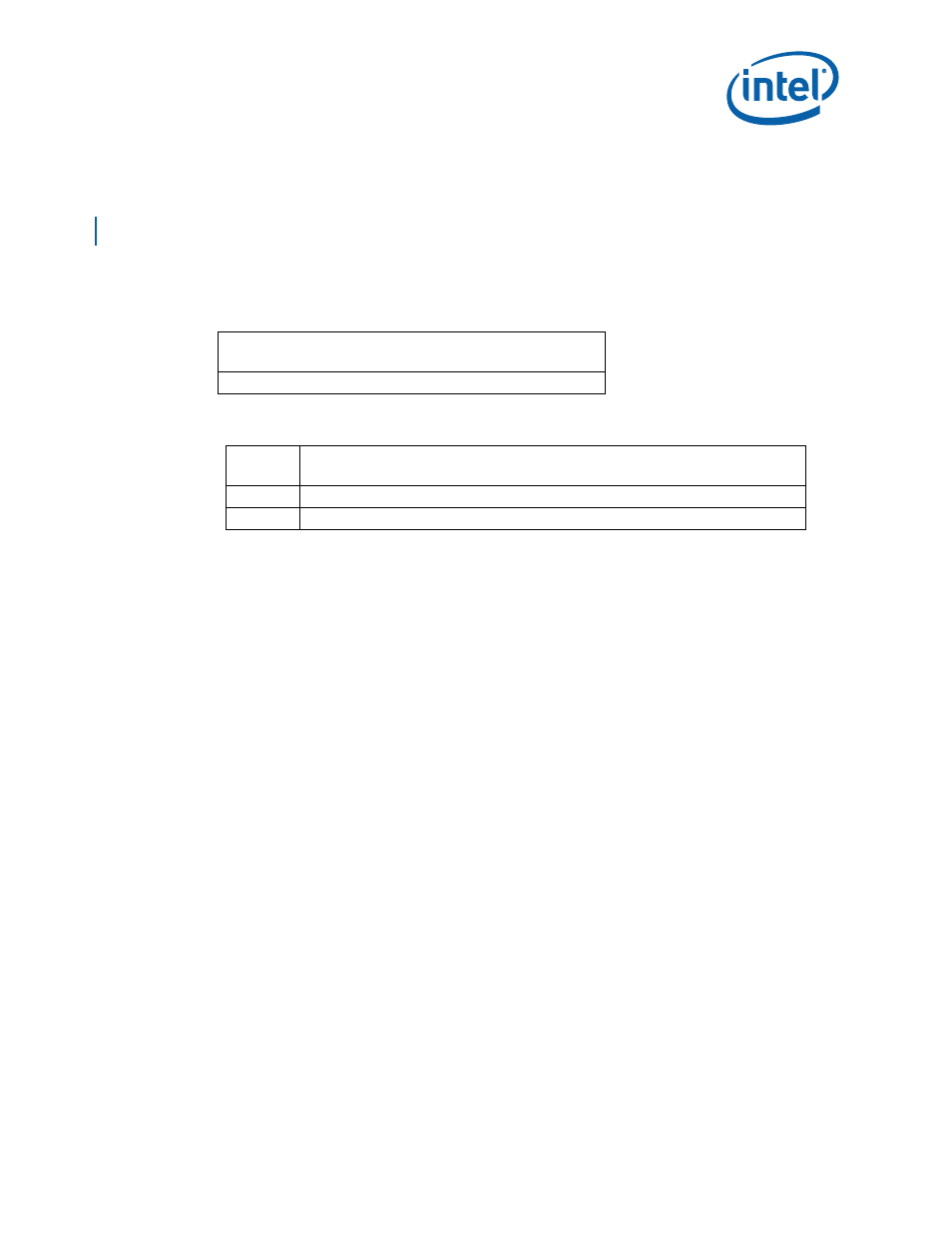

Table 486. PMON Internal Bus Memory Mapped Register Range Offsets

Internal Bus MMR Address Range Offset

(Relative to PMMRBAR)

+4 E000H

Table 487. PMON Register Summaries

Register

Offset

Register Name

+040h

PMON Feature Enable Register - PMONEN

+044h