H-matrix (indicates the single-bit error location), Intel – Intel CONTROLLERS 413808 User Manual

Page 524

Intel

®

413808 and 413812—SRAM Memory Controller

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

524

Order Number: 317805-001US

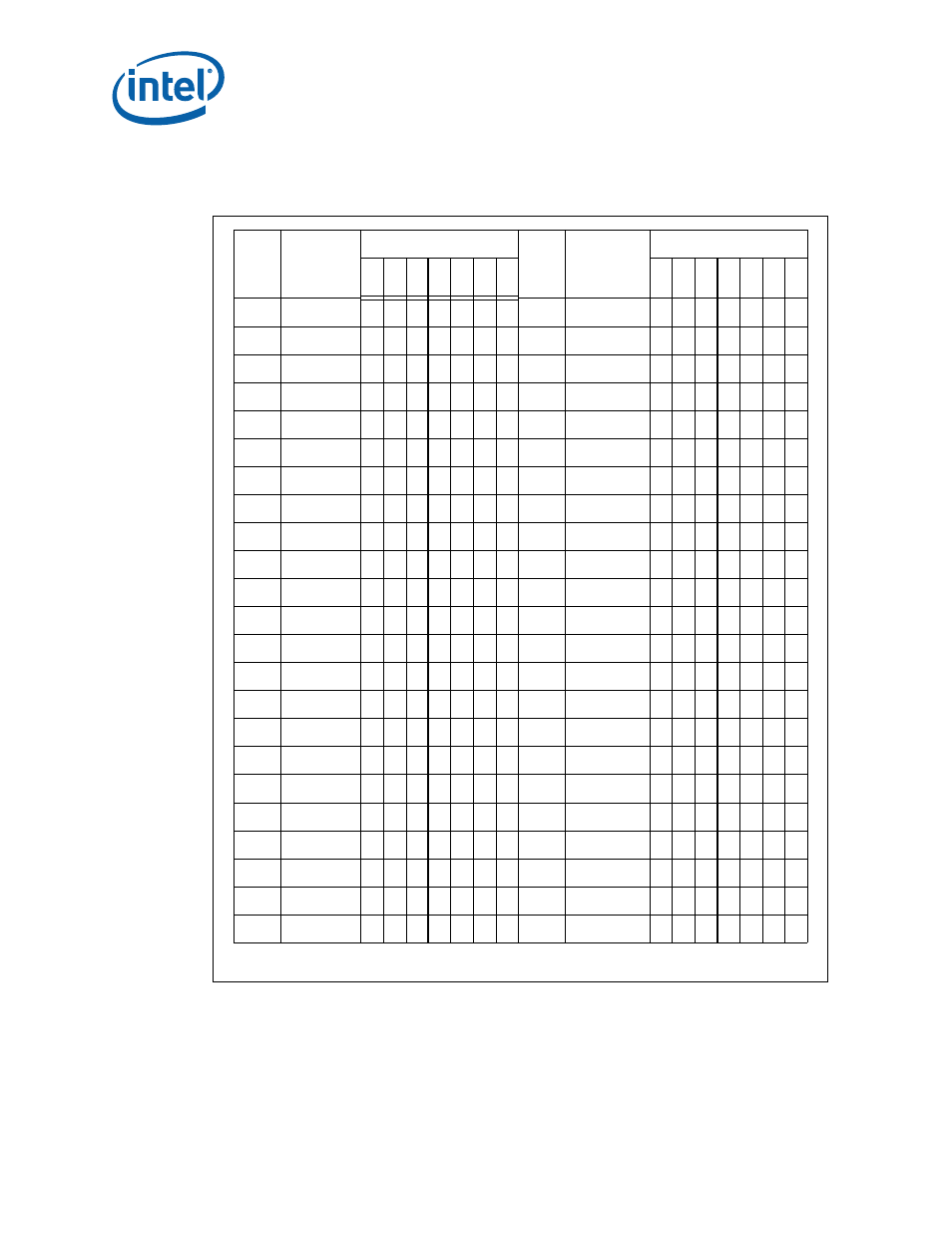

illustrates the H-Matrix used for decoding the syndrome. For single-bit errors,

the H-Matrix indicates the bit that contains the error and consequently, which bit to fix.

Figure 60. 4138xx

H-Matrix (indicates the single-bit error location)

Data

Bit

Syndrome

ECC Check Bits (E[6:0]

Data

Bit

Syndrome

ECC Check Bits (E[6:0]

E

6

E

5

E

4

E

3

E

2

E

1

E

0

E

6

E

5

E

4

E

3

E

2

E

1

E

0

E6

40H

X

D15

45H

X

X

X

E5

20H

X

D14

51H

X

X

X

E4

10H

X

D13

43H

X

X

X

E3

08H

X

D12

61H

X

X

X

E2

04H

X

D11

25H

X

X

X

E1

02H

X

D10

31H

X

X

X

E0

01H

X

D9

13H

X

X

X

D31

2CH

X

X

X

D8

5BH

X

X

X

X

X

D30

4AH

X

X

X

D7

46H

X

X

X

D29

1AH

X

X

X

D6

32H

X

X

X

D28

29H

X

X

X

D5

23H

X

X

X

D27

5EH

X

X

X

X

X

D4

68H

X

X

X

D26

6BH

X

X

X

X

X

D3

4CH

X

X

X

D25

2AH

X

X

X

D2

52H

X

X

X

D24

3BH

X

X

X

X

X

D1

62H

X

X

X

D23

64H

X

X

X

D0

49H

X

X

X

D22

26H

X

X

X

D21

3EH

X

X

X

X

X

D20

15H

X

X

X

D19

34H

X

X

X

D18

54H

X

X

X

D17

37H

X

X

X

X

X

D16

6EH

X

X

X

X

X