Table 446. uart register mmr addresses, 446 uart register mmr addresses – Intel CONTROLLERS 413808 User Manual

Page 669

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

669

UARTs—Intel

®

413808 and 413812

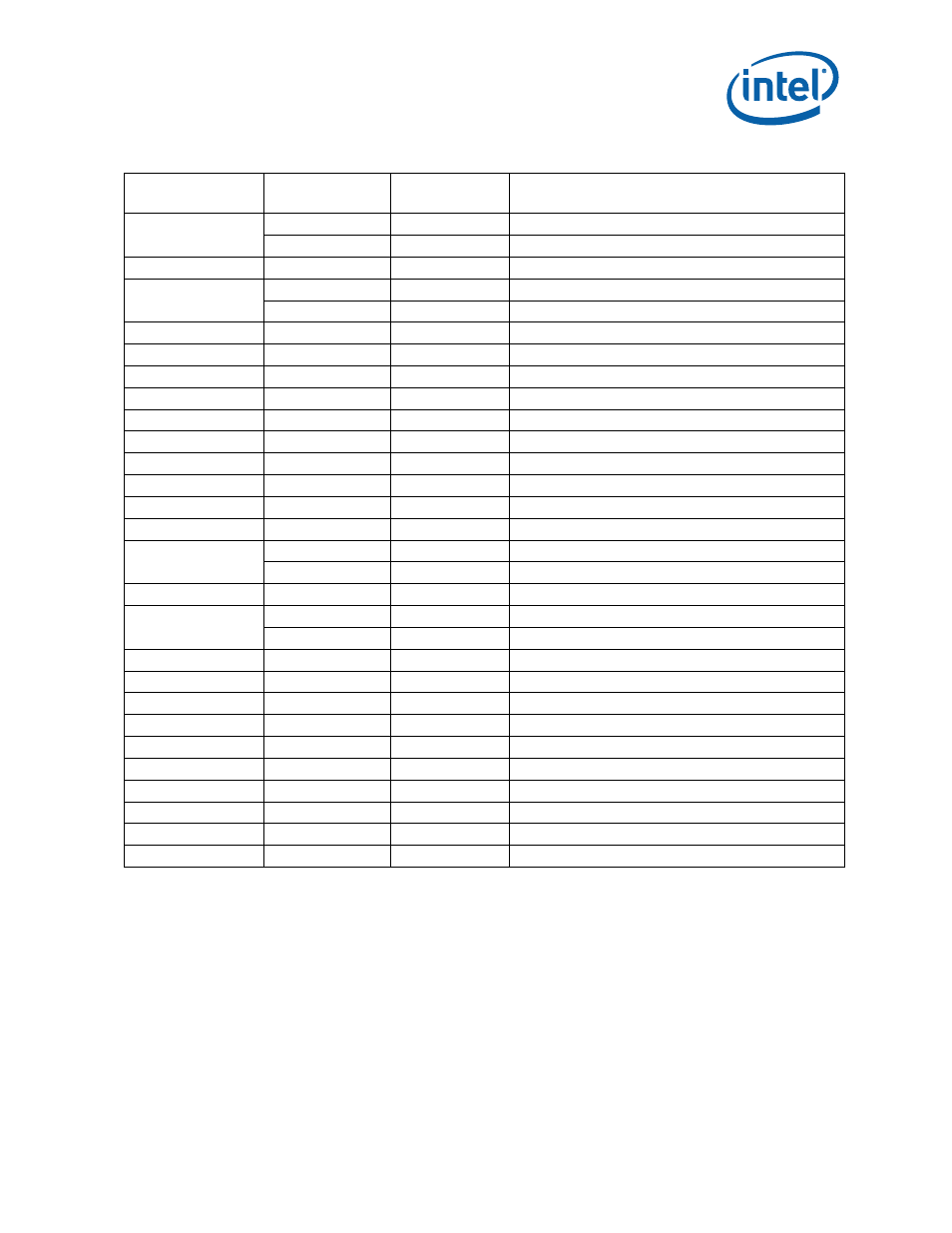

Table 446. UART Register MMR Addresses

UART Register

Addresses

DLAB Bit Value

Name

Register Accessed

+2300H

0

U0RBR

UART 0 Receive BUFFER (read only)

0

U0THR

UART 0 Transmit BUFFER (write only)

+2304H

0

U0IER

UART 0 Interrupt Enable (R/W)

+2308H

X

U0IIR

UART 0 Interrupt I.D. (read only)

X

U0FCR

UART 0 FIFO Control (write only)

+230CH

X

U0LCR

UART 0 Line Control (R/W)

+2310H

X

U0MCR

UART 0 Modem Control (R/W)

+2314H

X

U0LSR

UART 0 Line Status (Read only)

+2318H

X

U0MSR

UART 0 Modem Status (Read only)

+231CH

X

U0SPR

UART 0 Scratch Pad (R/W)

+2300H

1

U0DLL

UART 0 Divisor Latch (Low Byte, R/W)

+2304H

1

U0DLH

UART 0 Divisor Latch (High Byte, R/W)

+2324H

X

U0FOR

UART 0 FIFO Occupancy Register (R/W)

+2328H

X

U0ABR

UART 0 Autobaud Control Register (R/W)

+232CH

X

U0ACR

UART 0 Autobaud Count Register (read only)

+2340H

0

U1RBR

UART 1 Receive BUFFER (read only)

0

U1THR

UART 1 Transmit BUFFER (write only)

+2344H

0

U1IER

UART 1 Interrupt Enable (R/W)

+2348H

X

U1IIR

UART 1 Interrupt I.D. (read only)

X

U1FCR

UART 1 FIFO Control (write only)

+234CH

X

U1LCR

UART 1 Line Control (R/W)

+2350H

X

U1MCR

UART 1 Modem Control (R/W)

+2354H

X

U1LSR

UART 1 Line Status (Read only)

+2358H

X

U1MSR

UART 1 Modem Status (Read only)

+235CH

X

U1SPR

UART 1 Scratch Pad (R/W)

+2340H

1

U1DLL

UART 1 Divisor Latch (Low Byte, R/W)

+2344H

1

U1DLH

UART 1 Divisor Latch (High Byte, R/W)

+2364H

X

U1FOR

UART 1 FIFO Occupancy Register (R/W)

+2368H

X

U1ABR

UART 1 Autobaud Control Register (R/W)

+236CH

X

U1ACR

UART 1 Autobaud Count Register (read only)