6 localtohost control/status register - l2h_csr, 304 localtohost control/status register - l2h_csr, Sram dma unit (sdma)—intel – Intel CONTROLLERS 413808 User Manual

Page 451: Bit default description, Reserved, Intel

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

451

SRAM DMA Unit (SDMA)—Intel

®

413808 and 413812

5.4.6

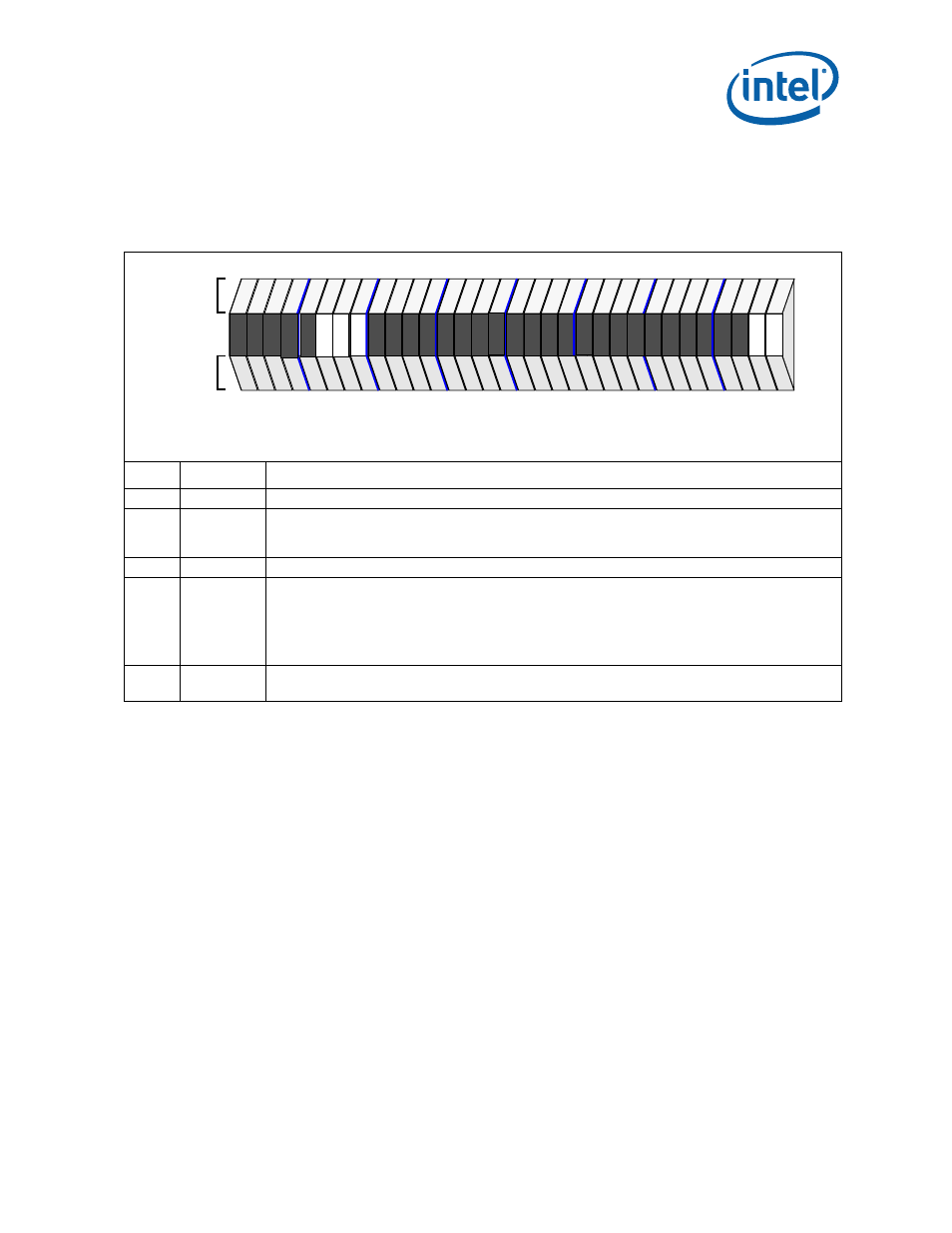

LocalToHost Control/Status Register - L2H_CSR

The LocalToHost Control/Status Register (L2H_CSR) provides the control and status for

the LocalToHost channel.

Table 304. LocalToHost Control/Status Register - L2H_CSR

Bit

Default

Description

31:27

00000

2

Reserved

26:24

000

2

Error Flags - Read/Clear

One or more of these bits is set to indicate an error has occurred with the DMA operation. The precise

cause of the error is determined by reading the ATU or XSISC error registers.

23:02

0000H

Reserved

01

0

2

Channel Go (CHGO) - Read/Set

Set this bit to begin the DMA operation.

This bit must be cleared while the DMA registers are being set up. The CHGO bit is set by firmware to

begin the DMA operation. When the DMA operation begins the hardware clears this bit. Note that

clearing of this bit does not indicate the DMA operation is complete, rather that the hardware has

started processing it.

00

0

2

Enable Register - Read/Write

Must be set for proper operation. A value of zero (when the CHGO bit is set) has unpredictable results.

Coprocessor

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rc

na

rv

na

rc

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rc

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rw

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rs

na

rw

na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Internal bus address offset

1823CH