6 outbound doorbell register - odr, Table 271. outbound doorbell register - odr, 271 outbound doorbell register - odr – Intel CONTROLLERS 413808 User Manual

Page 416: Intel, Bit default description, P_intd, P_intc, P_intb, P_inta

Intel

®

413808 and 413812—Messaging Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

416

Order Number: 317805-001US

4.7.6

Outbound Doorbell Register - ODR

The Outbound Doorbell Register (ODR) allows software interrupt generation. It allows

the Intel XScale

®

processor to generate Host I/O Interface interrupts to the host

processor by writing to the Software Interrupt bits or to a specific Host I/O Interface

interrupt bit. The generation of Host I/O Interface interrupts through the Outbound

Doorbell Register may be masked by setting the Outbound Doorbell Interrupt Mask bit

in the Outbound Interrupt Mask Register.

The Software Interrupt bits in this register can only be set by the Intel XScale

®

processor and can only be cleared by an external Host I/O Interface agent.

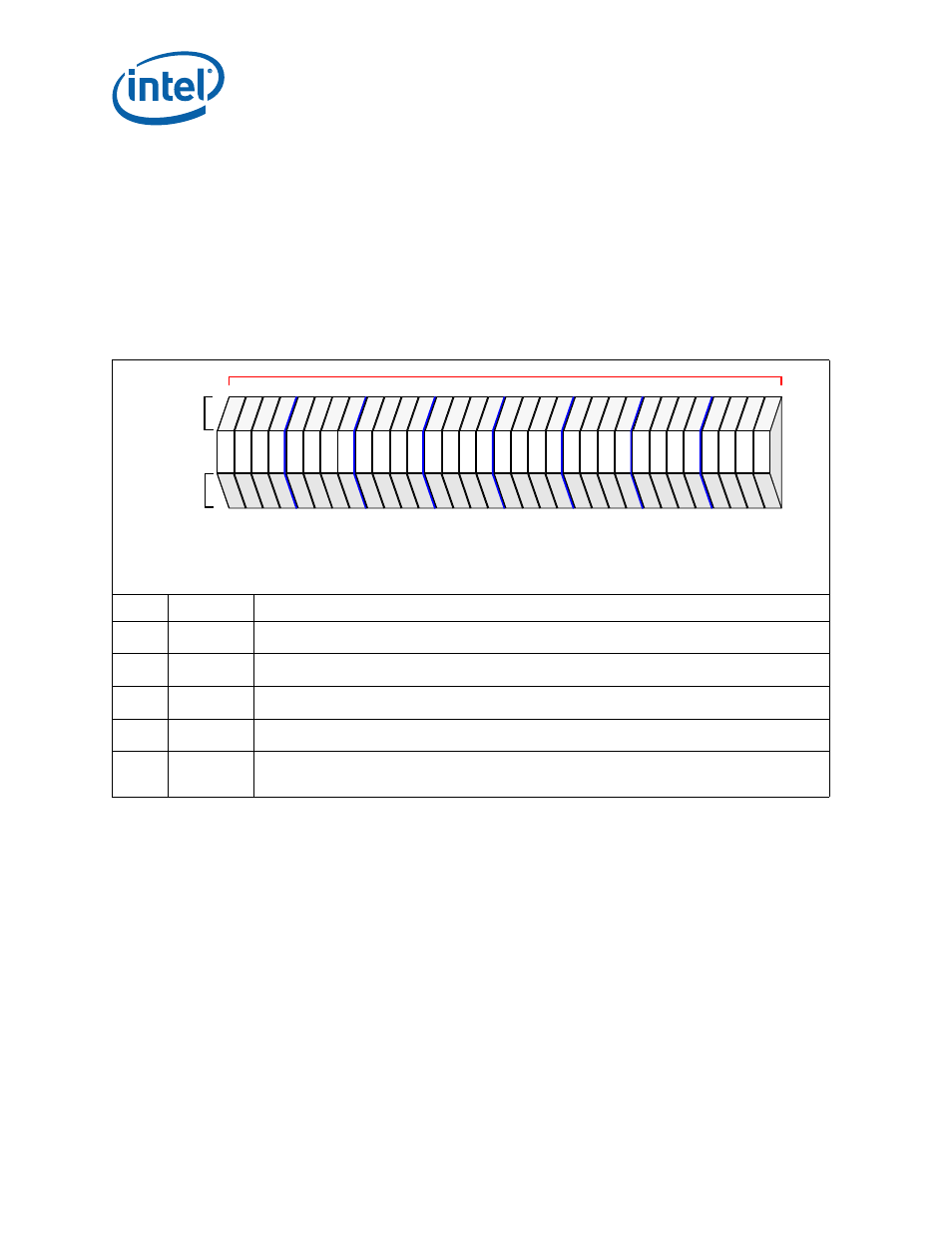

Table 271. Outbound Doorbell Register - ODR

Bit

Default

Description

31

0

2

PCI Interrupt D - When set, this bit causes the

P_INTD#

signal to be asserted or a Message-signaled

Interrupt is generated (when enabled). When this bit is cleared, the

P_INTD#

signal is deasserted.

30

0

2

PCI Interrupt C - When set, this bit causes the

P_INTC#

signal to be asserted or a Message-signaled

Interrupt is generated (when enabled). When this bit is cleared, the

P_INTC#

signal is deasserted.

29

0

2

PCI Interrupt B - When set, this bit causes the

P_INTB#

signal to be asserted or a Message-signaled

Interrupt is generated (when enabled). When this bit is cleared, the

P_INTB#

signal is deasserted.

28

0

2

PCI Interrupt A - When set, this bit causes the

P_INTA#

signal to be asserted or a Message-signaled

Interrupt is generated (when enabled). When this bit is cleared, the

P_INTA#

signal is deasserted.

27:00

000000H

Software Interrupt - When any bit is set, generate a PCI interrupt or a Message-signaled interrupt is

generated (when enabled). The PCI interrupt pin used is determined by the ATU Interrupt Pin Register.

When all bits are clear, do not generate a PCI interrupt.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

rs

rc

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

MU/PCI Base Address Offset

ODR: 002CH

internal bus address offset

ODR: 402CH