Intel CONTROLLERS 413808 User Manual

Page 703

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

703

I

2

C Bus Interface Units—Intel

®

413808 and 413812

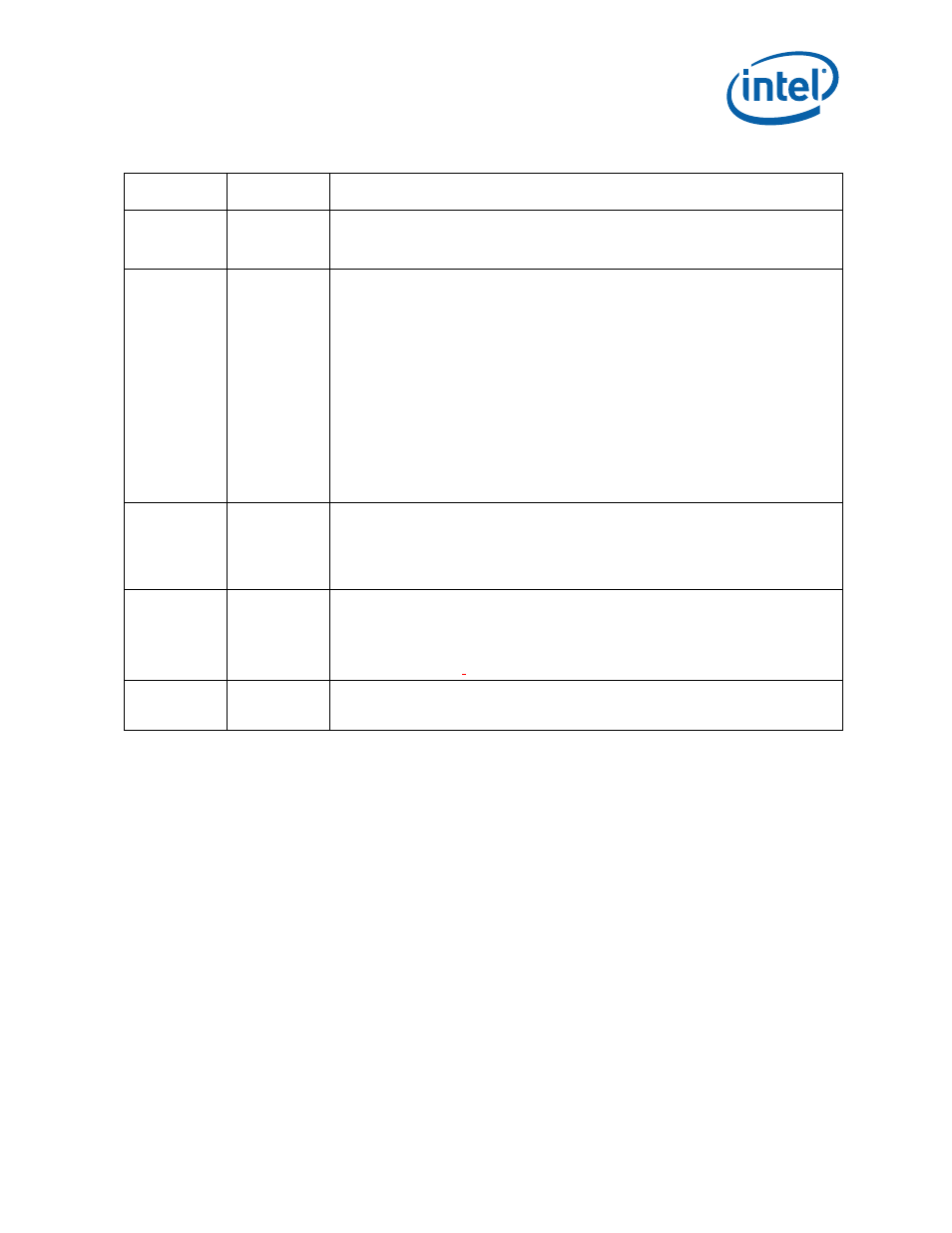

Wait for

Acknowledge

from

slave-receiver

Master-transmit

only

• As a master-transmitter, the I

2

C Bus Interface Unit generates the clock for the

acknowledge pulse. The I

2

C Bus Interface Unit is responsible for releasing the

SDA

line

to allow slave-receiver Ack transmission.

• See

.

Read one byte of

I

2

C Data from

the IDBR

Master-receive

only

• Data receive mode of I

2

C master operation.

• Eight bits are read from the serial bus, collected in the shift register then transferred to

the IDBR after the Ack/Nack bit is read.

• The Intel XScale

®

processor reads the IDBR when the IDBR Receive Full bit is set and

the Transfer Byte bit is clear. When enabled, a IDBR Receive Full Interrupt is signalled to

the Intel XScale

®

microarchitecture.

• When the IDBR is read, when the Ack/Nack Status is clear (indicating Ack), the Intel

XScale

®

processor writes the Ack/Nack Control bit and set the Transfer Byte bit to

initiate the next byte read.

• When the Ack/Nack Status bit is set (indicating Nack), Transfer Byte bit is clear, STOP

bit in the ICR is set, and Unit Busy bit in the ISR is set, then the last data byte has been

read into the IDBR and the I

2

C Bus Interface Unit is sending the STOP.

• When the Ack/Nack Status bit is set (indicating Nack), Transfer Byte bit is clear, but the

STOP bit is clear, then the Intel XScale

®

processor has two options: 1. set the START

bit, write a new target address to the IDBR, and set the Transfer Byte bit which sends a

repeated start condition, 2. set the Master Abort bit and leave the Transfer Byte clear

which sends a STOP only.

Transmit

Acknowledge to

slave-transmitte

r

Master-receive

only

• As a master-receiver, the I

2

C Bus Interface Unit generates the clock for the

acknowledge pulse. The I

2

C Bus Interface Unit is also responsible for driving the

SDA

line during the Ack cycle.

• When the next data byte is to be the last transaction, the Intel XScale

®

processor sets

the Ack/Nack Control bit for Nack generation.

• See

.

Generate a

Repeated START

to chain I

2

C

transactions

Master-transmit

Master-receive

• When data chaining is desired, a repeated START condition is used instead of a STOP

condition.

• This occurs after the last data byte of a transaction has been written to the bus.

• The Intel XScale

®

processor writes the next target slave address and the R/W# bit to

the IDBR, set the START bit, and set the Transfer Byte bit.

• See

.

Generate a STOP Master-transmit

Master-receive

• Generated after the Intel XScale

®

processor writes the last data byte on the bus.

• Intel XScale

®

processor generates a STOP condition by setting the STOP bit in the ICR.

• See

.

Table 467. Master Transactions (Sheet 2 of 2)

I

2

C Master

Action

Mode of

Operation

Definition