28 interrupt priority register 3 - ipr3, Table 410. interrupt priority register 3 - ipr3, 28interrupt priority register 3 — ipr3 – Intel CONTROLLERS 413808 User Manual

Page 622: 410 interrupt priority register 3 — ipr3, 28 interrupt priority register 3 — ipr3

Intel

®

413808 and 413812—Interrupt Controller Unit

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

Developer’s Manual

October 2007

622

Order Number: 317805-001US

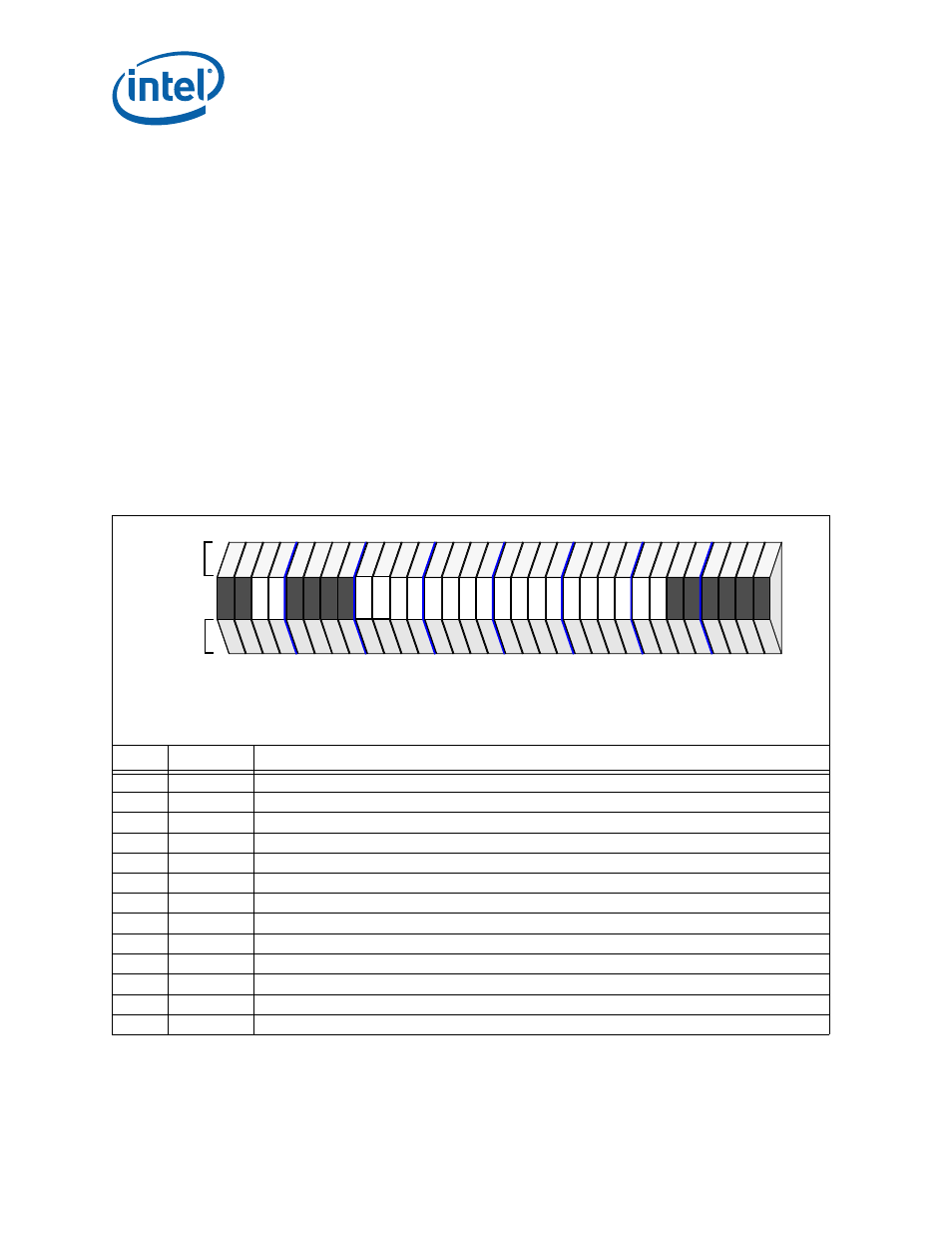

10.7.28 Interrupt Priority Register 3 — IPR3

The Interrupt Priority Register 3 is a 32-bit Coprocessor 6 control register used to

assign a priority level to interrupt sources 63 down to 48. The IPR3 control register is

used to assign one of 4 priority levels to each interrupt source independent of the

INTSTR[3:0] registers:

When interrupt vector generation is enabled and there are multiple requests pending

either in the FINTSRC[3:0] or the IINTSRC[3:0] registers, the highest priority vectors

pending for either FIQ or IRQ are presented in the FINTVEC or IINTVEC respectively.

Note:

When multiple interrupts at the same priority level are pending for either FIQ or IRQ,

the vector is selected according to a fixed priority based on bit location. Highest order

bit is first.

00

2 —

High Priority

01

2 —

Medium/High Priority

10

2 —

Medium/Low Priority

11

2 —

Low Priority

Table 410. Interrupt Priority Register 3 — IPR3

Bit

Default

Description

31:30

00

2

Reserved.

29:28

00

2

Messaging Unit Error Interrupt Priority

27:24

00

2

Reserved.

23:22

00

2

Reserved.

21:20

00

2

Reserved.

19:18

00

2

Reserved.

17:16

00

2

Memory Controller Unit Error Interrupt Priority

15:14

00

2

ATU Error Interrupt Priority

13:12

00

2

ATU Configuration Register Write Interrupt Priority

11:10

00

2

Peripheral Bus Interface Unit Error Interrupt Priority

9:8

00

2

UART 1 Interrupt Priority

7:6

00

2

UART 0 Interrupt Priority

5:0

00 0000

2

Reserved.

Memory

Coprocessor

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na na

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible

Intel XScale

®

processor Coprocessor address

CP6, Page 8, Register 3