2 i2c status register x - isrx, 472 i, C status register – Intel CONTROLLERS 413808 User Manual

Page 717: Table 472. i, C status register x — isrx (sheet 1 of 2), C bus interface units—intel, Bit default description, Bus error detected, Slave address detected, General call address detected

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

717

I

2

C Bus Interface Units—Intel

®

413808 and 413812

14.8.2

I

2

C Status Register

x —

ISR

x

I

2

C interrupts are signalled to the 4138xx interrupt controller by the I

2

C Interrupt

Status Register (ISRx). Software uses the ISR bits to check the status of the I

2

C unit

and bus. ISRx bits (bits 9-5) are updated after the Ack/Nack bit has completed on the

I

2

C bus.

The ISRx is also used to clear interrupts signalled from the I

2

C Bus Interface Unit.

These are:

• IDBRx Receive Full

• IDBRx Transmit Empty

• Slave Address Detected

• Bus Error Detected

• STOP Condition Detect

• Arbitration Lost

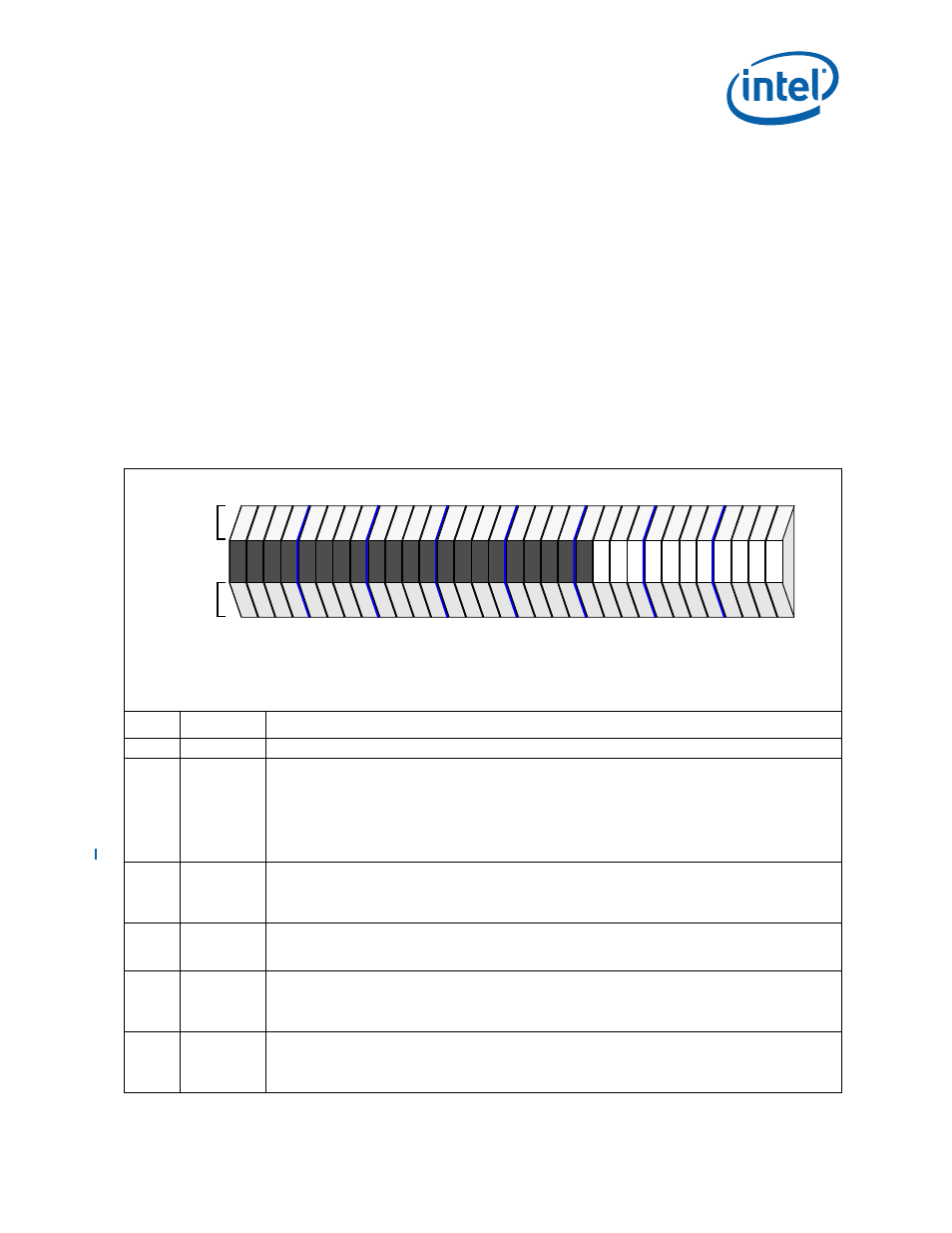

Table 472. I

2

C Status Register x — ISRx (Sheet 1 of 2)

Bit

Default

Description

31:11

000000H Reserved

10

0

2

Bus Error Detected

:

0 = No error detected.

1 = The I

2

C unit sets this bit when it detects one of the following error conditions:

• As a master transmitter, no Ack was detected on the interface after a byte was sent.

• As a slave receiver, the I

2

C unit generates a Nack pulse.

Note:

When an error occurs, I

2

C bus transactions continue. Software must insure that misplaced

START and STOP conditions do not occur. See

Section 14.3.3, “Arbitration” on page 700

.

09

0

2

Slave Address Detected

:

0 = No slave address detected.

1 = I

2

C unit detected a 7-bit address that matches the general call address or ISAR. An interrupt is

signalled when enabled in the ICR.

08

0

2

General Call Address Detected

:

0 = No general call address received.

1 = I

2

C unit received a general call address.

07

0

2

IDBR Receive Full

:

0 = The IDBR has not received a new data byte or the I

2

C unit is idle.

1 = The IDBR register received a new data byte from the I

2

C bus. An interrupt is signalled when

enabled in the ICR.

06

0

2

IDBR Transmit Empty

:

0 = The data byte is still being transmitted.

1 = The I

2

C unit has finished transmitting a data byte on the I

2

C bus. An interrupt is signalled when

enabled in the ICR.

PCI

IOP

Attributes

Attributes

28

24

20

16

12

8

4

0

31

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rv

na

rc

na

rc

na

rc

na

rc

na

rc

na

rc

na

rc

na

ro

na

ro

na

ro

na

ro

na

Unit #

0

1

2

Intel XScale

®

processor internal bus address

offset

+2504H

+2524H

+2544H

Attribute Legend:

RV = Reserved

PR = Preserved

RS = Read/Set

RW = Read/Write

RC = Read Clear

RO = Read Only

NA = Not Accessible