3 start and stop bus states, Table 466. start and stop bit definitions, Figure 93. start and stop conditions – Intel CONTROLLERS 413808 User Manual

Page 695: 93 start and stop conditions, 466 start and stop bit definitions, The i, Lines for a start and stop condition

Intel

®

413808 and 413812 I/O Controllers in TPER Mode

October 2007

Developer’s Manual

Order Number: 317805-001US

695

I

2

C Bus Interface Units—Intel

®

413808 and 413812

14.2.3

Start and Stop Bus States

The I

2

C bus defines a transaction START and a transaction STOP bus state that are

used at the beginning and end of the transfer of one to an unlimited number of bytes

on the bus.

The 4138xx uses the START and STOP bits in the I

2

C Control Register (ICR) to:

• initiate an additional byte transfer

• initiate a START condition on the I

2

C bus

• enable Data Chaining (repeated START)

• initiate a STOP condition on the I

2

C bus

summarizes the definition of the START and STOP bits in the ICR.

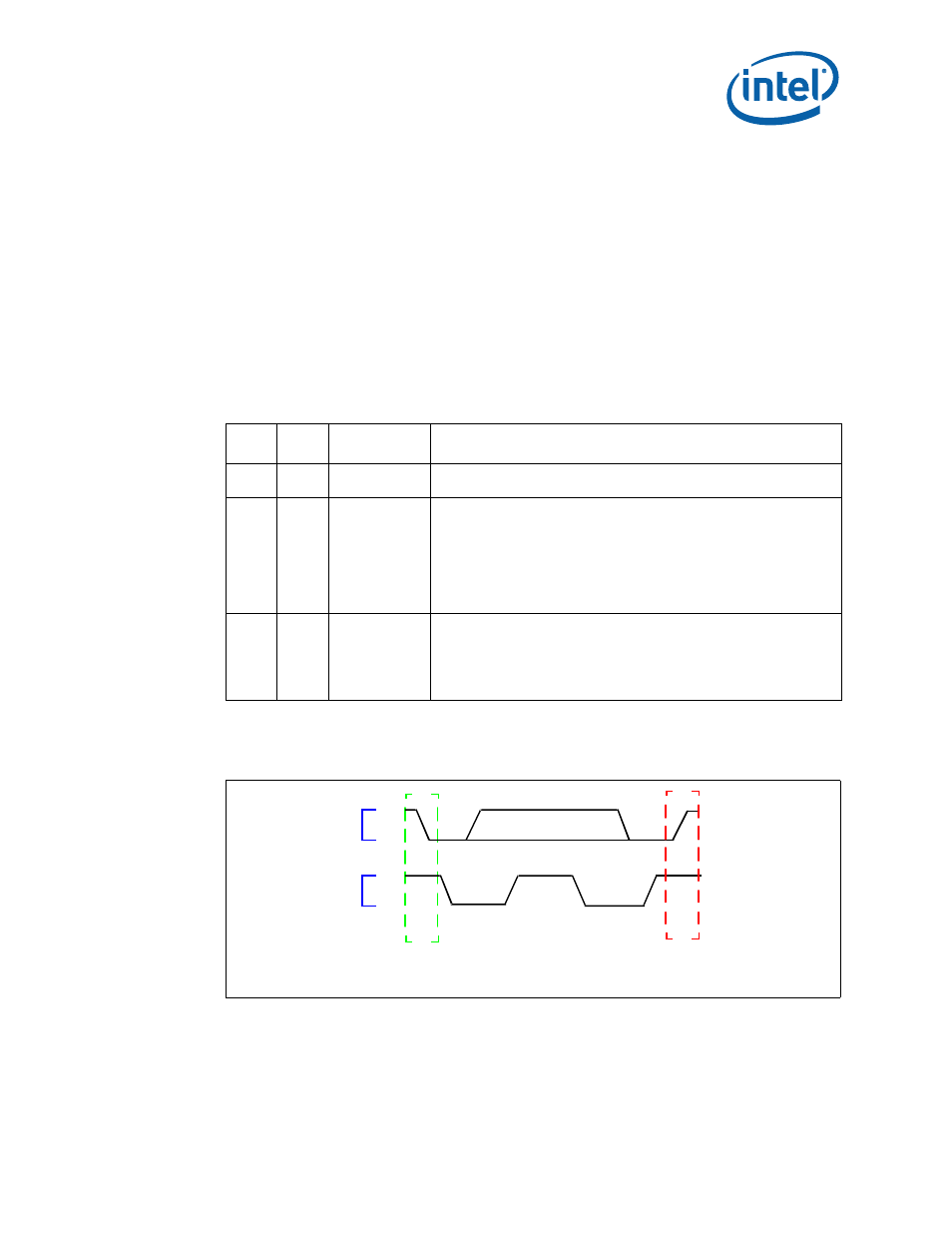

shows the relationship between the

SDA

and

SCL

lines for a START and STOP

condition.

Table 466. START and STOP Bit Definitions

STOP

bit

STAR

T bit

Condition

Notes

0

0

No START or

STOP

• No START or STOP condition is sent by the I

2

C Bus Interface Unit.

This is used when multiple data bytes need to be transferred.

0

1

START Condition

and

Repeated START

• The I

2

C Bus Interface Unit sends a START condition and transmit the

contents of the 8 bit IDBR after the START. The IDBR must contain

the 7-bit address and the R/W# bit before a START is initiated.

• For a repeated start, the IDBR contents contains the target slave

address and the R/W# bit. This enables multiple transfers to

different slaves without giving up the bus.

• The interface stays in Master-Transmit mode when a write is used or

transition to master-receive mode when a read is requested.

1

X

STOP Condition

• In Master-Transmit mode, the I

2

C Bus Interface Unit transmits the

8-bit IDBR and then send a STOP on the I

2

C bus.

• In Master-Receive mode, the Ack/Nack Control bit in the ICR must

be changed to a negative Ack (see

). The I

2

C Bus

Interface Unit writes the Nack bit (Ack/Nack Control bit must be 1),

receive the data byte in the IDBR, then send a STOP on the I

2

C bus.

Figure 93. Start and Stop Conditions

SDA

SCL

Start Condition

~

~

~

~

~

~

Stop Condition

B6283-01